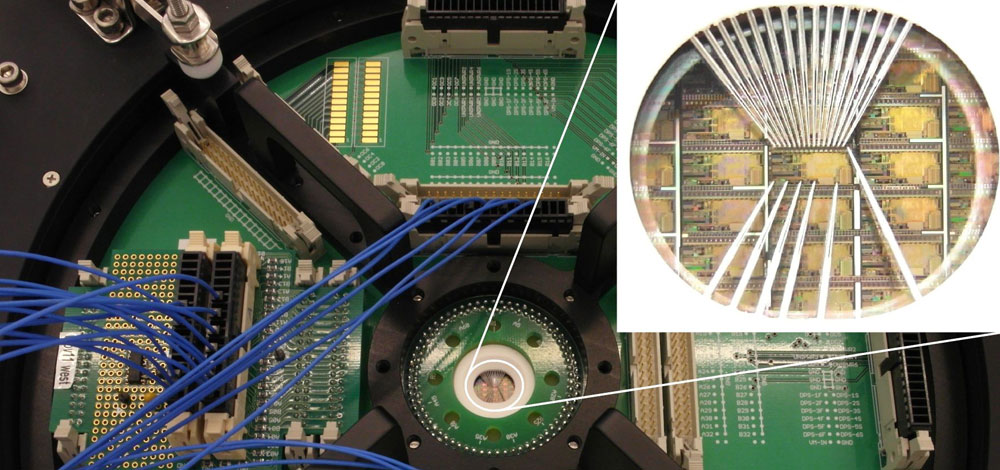

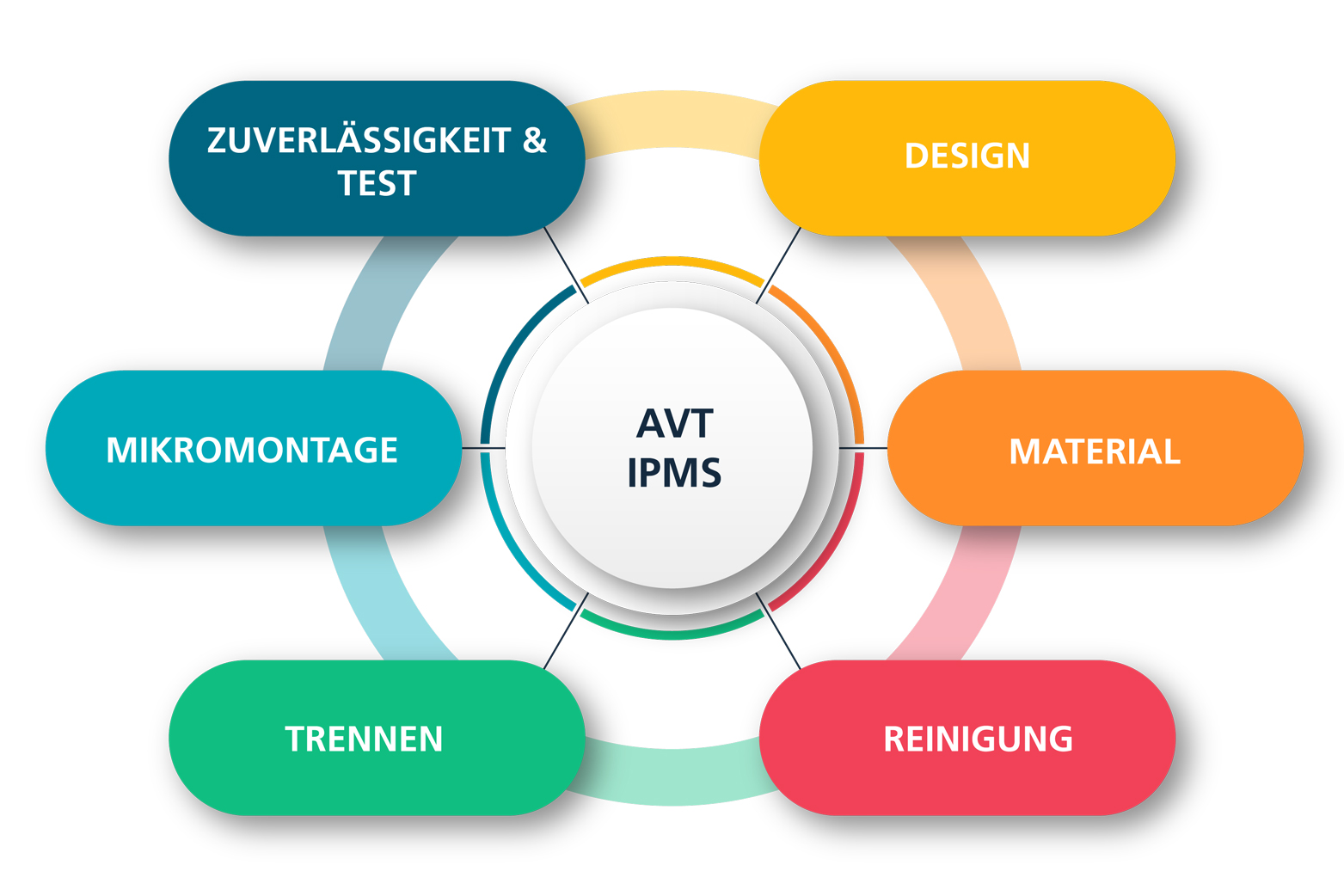

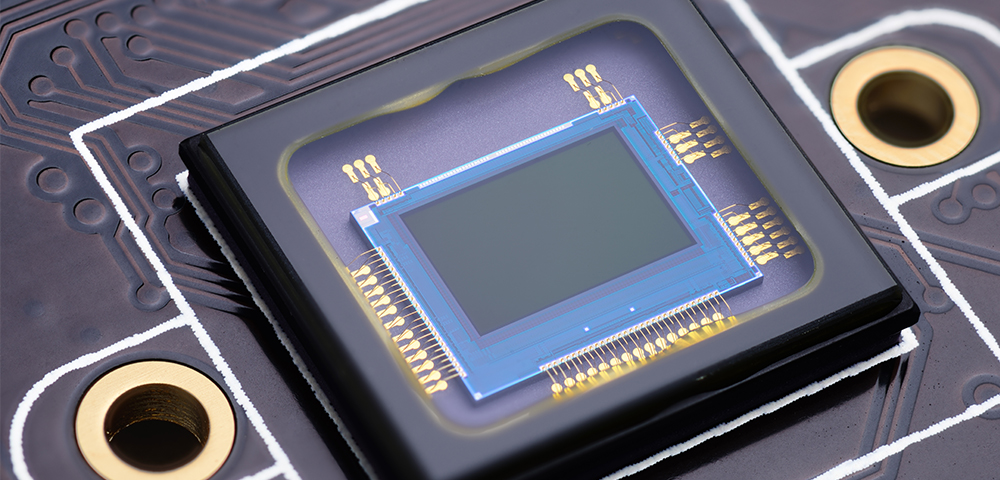

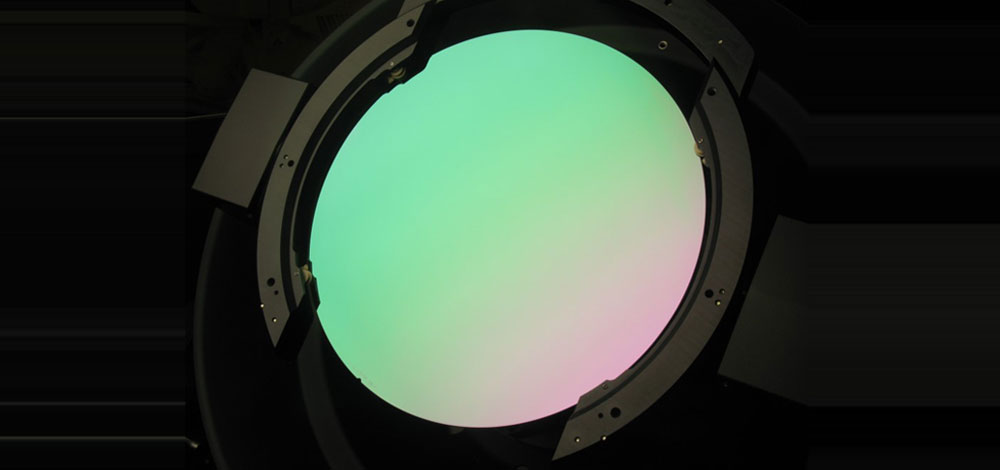

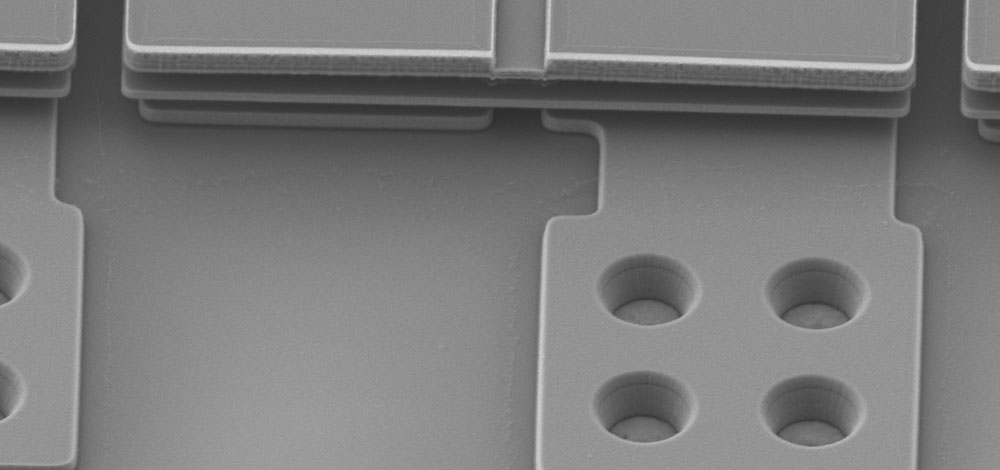

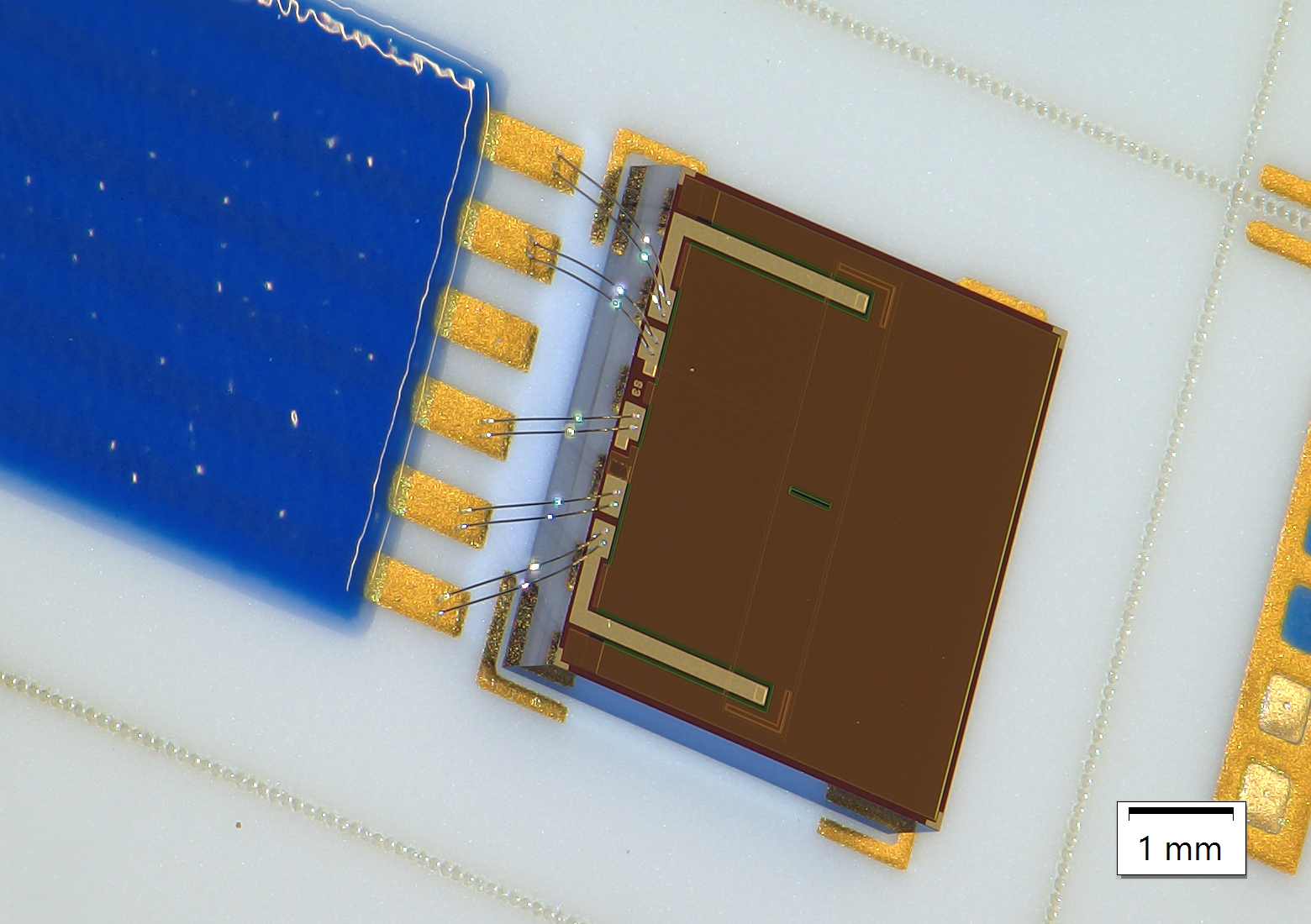

Der Entwurf anwendungsspezifischer integrierter Schaltungen ermöglicht hochkomplexe mikroelektronische Bauelemente, z. B. Mikrodisplays und optoelektronische Sensoren. Die Methodik dieses Entwurfs basiert auf Schaltungssimulation, Layoutentwurf und Verifikation. Wir erstellen solche Entwürfe mit industriekompatiblen Software-Werkzeugen und implementieren diese in gemischt analog/digitale CMOS-Prozesse von Silizium-Wafer-Herstellern weltweit. Nach der Fertigung der Silizium-Wafer werden die Funktionalität mittels Wafer- und Bauelement-Tests verifiziert und Prototypen erstellt. Projektspezifisch kann danach die Überführung in (Pilot-)Fertigung erfolgen.

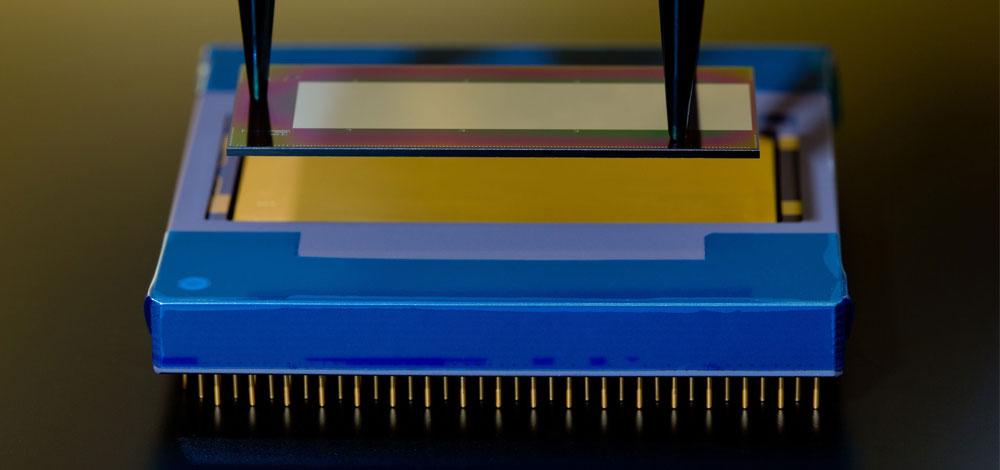

Eine Alleinstellung besitzen wir im Entwurf mikroelektronischer Schaltungen und Bauelemente mit anwendungs- und kundenspezifischen Adaptionen der CMOS-Prozesse beim Waferhersteller, um diese Wafer anschließend einer Weiterverarbeitung, z. B. der OLED-Beschichtung zuzuführen. Diese Weiterverarbeitung ergänzt vor allem photonische oder optische Komponenten zur Silizium-CMOS-Waferfunktionalität, z. B. für hochauflösende OLED-Mikrodisplays.

- Entwurf mikroelektronischer Schaltungen und Bauelemente mit anwendungsspezifischer Adaption der CMOS-Prozesse

- Industriekompatible Schaltungssimulation, Layoutentwurf und Verifikation

- Implementierung in gemischt analog/digitale CMOS-Prozesse der Silizium-Wafer-Hersteller

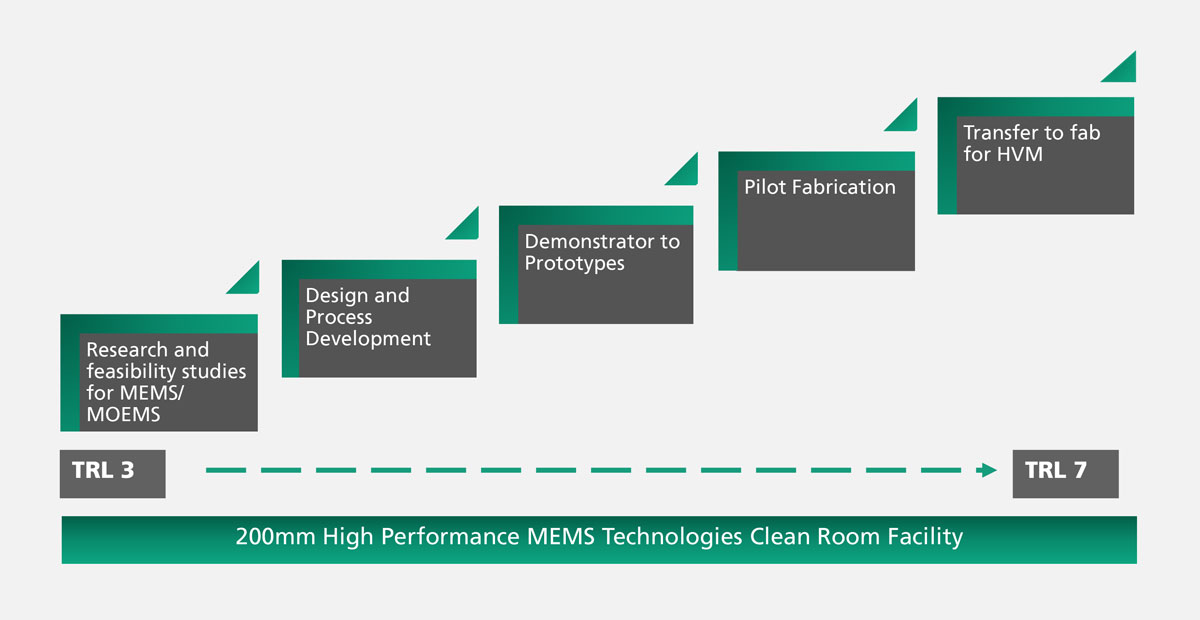

- Prototypenfertigung, Überführung in (Pilot-)Fertigung

Fraunhofer-Institut für Photonische Mikrosysteme

Fraunhofer-Institut für Photonische Mikrosysteme