In der Volumenproduktion von Mikroprozessoren spielt die Verdrahtungsebene eine tragende Rolle um die Performance, die Energieeffizienz und die Verlässlichkeit des Systems zu gewährleisten. Die Metallisierung der einzelnen Ebenen wird in verschiedenen Modulen realisiert in dem Lithographie-, Ätz-, Reinigungs-, Dünnschicht-, Galvanik-, Ofen- und Polierprozesse eine große Rolle spielen.

Am Fraunhofer IPMS kann diese komplette Prozesslinie abgebildet und einzeln untersucht werden. Der Fokus dabei liegt auf der Kupfermetallisierung. Dabei werden im Damascene-Prozess die geätzten Strukturen mit der Barriere und Kupferkeimschicht ausgekleidet, um im folgenden Plating-Schritt, diese mit Kupfer elektrochemisch durch einen Bottom-up-Fill, den sog. Superfill, aufzufüllen. Nach einem Ofenprozess, indem größere Kupferkristallkörner ausgebildet werden folgt der CMP-Schritt (chemisch-mechanisches Planarisieren), indem das überschüssige Kupfer wegpoliert wird um die Einzelnen Leiterbahnen im Nachgang voneinander zu isolieren und eine einheitliche Höhe zu schaffen. Angepasste Reinigungsprozesse tragen dabei sowohl vor dem Metallisieren (Post Etch Clean) als auch nach dem Polieren (Post Polish Clean) dazu bei möglichst defektfreie Ebenen zu erzeugen.

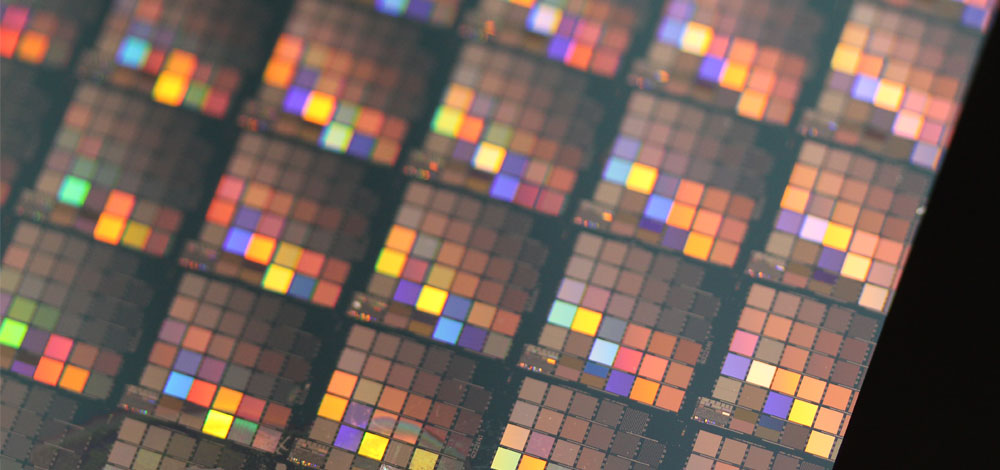

Jeder dieser Schritte hat seine eigenen Herausforderung, die am Fraunhofer IPMS an 300 mm Wafern in den jeweiligen Modulen in einem industriellen und wissenschaftlichen Umfeld im Zusammenspiel mit eigenen State-of-the-Art Anlagen und Materialherstellern als auch mit IC-Herstellern und im Wissen über aktuelle Entwicklungen zu Prozessen in 28 nm und 22 nm Technologieknoten und darüber hinaus, angegangen werden

Fraunhofer-Institut für Photonische Mikrosysteme

Fraunhofer-Institut für Photonische Mikrosysteme