FRAUNHOFER INSTITUTE FOR PHOTONIC MICROSYSTEMS IPMS

# OFET-SUBSTRATES FOR THE CHARACTERIZATION OF ORGANIC SEMICONDUCTOR MATERIALS

Fraunhofer Institute for Photonic Microsystems IPMS

Maria-Reiche-Str. 2 01109 Dresden

### Contact

Dipl. Wi.-Ing. Fritz Herrmann Technical Sales Manager

+49 351 88 23 4612 fritz.herrmann@ipms.fraunhofer.de

www.ipms.fraunhofer.de

Organic electronics have become a keyword for new types of applications based on organic semiconductors and other materials that can easily be processed. Typical for this new class of materials are low temperature processes and large area deposition and structuring with various coating and printing processes. The active semiconductor materials determine the performance of the entire system considerably. That is why a simple and reliable electronic characterization of these semiconductors is not only an essential prerequisite for material development in the labs of organic chemists but also for process developers and circuit designers.

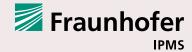

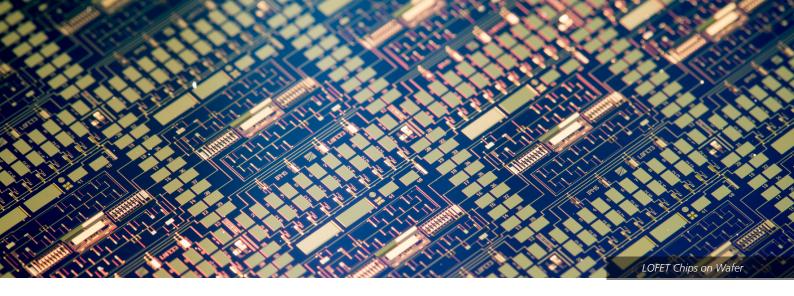

Fraunhofer IPMS provides standardized single transistor structures in bottom gate architecture. These substrates for organic field effect transistors (OFETs) are produced in the clean room on silicon wafers with thermal silicon dioxide (SiO<sub>2</sub>) as full-area dielectrics and gold electrodes in lift-off technology. This is a significant advantage with respect to reliability and reproducibility that enables the application of these substrates for quality assurance in major chemical corporations. The spectrum of possible customers ranges from universities, independent research institutions to industrial customers. The OFET substrates are used for

research purposes in the field of materials testing or quality control. They are essential for organic materials development.

The Fraunhofer IPMS offers different standard solutions and realizes customer-specific modifications by tailoring the samples with respect to chip size, design, and layer thickness of the thermal oxide. In order to simplify the measurement procedures of OFET substrates, the Fraunhofer IPMS has also developed a hand prober. This OFET miniprober allows fast and easy measurements by reliable pad contacting.

0721002RR FMT OFFT IOFFT FN 2021-02

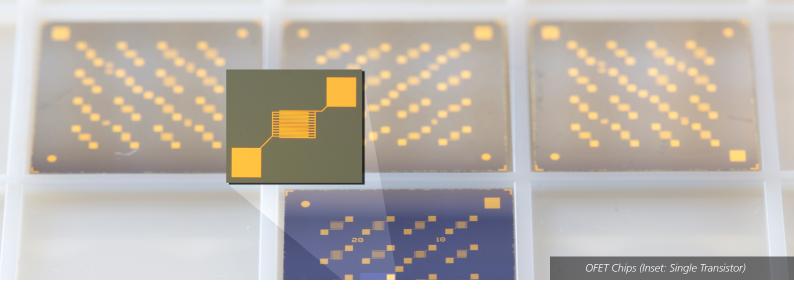

1 OFET Chip Layout

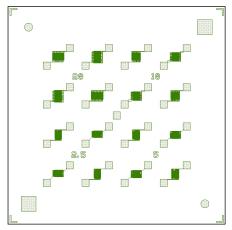

2 OFET wafer stack

#### **ORGANIC FIELD EFFECT TRANSISTORS (OFET)**

If an organic semiconductor layer is deposited on such a substrate, the Si-bulk acts as gate electrode and controls the channel current between the gold electrodes on top. A suitably doped Si-SiO<sub>2</sub> interface in CMOS quality guarantees a reproducible gate contact. Gold electrodes with a patented undercoating suppress the formation of injector barriers between the gold electrodes and the organics in the transistor channel. This guarantees reliable ohmic source / drain contacts in the OFET even for p-type semiconductors. Due to both reliability and reproducible preparation, these substrates are applied for standardized material screening by all key developers of organic semiconductors all over the world.

In the standard OFET layout, a 200 mm wafer has almost 1800 individual transistors on 112 chips, each sized at 15 × 15 mm². Each chip carries four groups with four identical transistors, with a channel length of 2.5, 5, 10, 20 µm respectively (Figure 2). Identical layouts with graded channel widths as well as a flexible selection of the oxide thickness allow the adjustment to a broad voltage and conductivity range of the test materials. Customer-specific layouts with different electrode geometries are possible at any time. In advantage for our customers, beside the wafers we offer waffle packs with 16 seperated chips.

1 OFET Miniprober

## THE OFET MINIPROBER

In order to simply and quickly measure OFET components with a given substrate size, pad grid and pad arrangement large batches, Fraunhofer **IPMS** has developed a miniprober (Figure 1). It has two electric connections on the front (source and drain) and one connection on the back (gate) and does not require probe station, samplers or manipulator pins. A reliable interconnection is established on contact pads, which are only  $0.5 \times 0.5$  mm<sup>2</sup> in size. Customized versions of the miniprober varying the connection arrangement, the position and number of the pads are possible. This makes the miniprober suitable for other applications in

addition to OFETs. Signals are transmitted to the measurement instrument by BNC or triax cables.

# Advantages of the OFET Miniprober

- No probing system required

- Easy DUT handling

- Stable and secure connection

- Other chip sizes or pad arrangements possible

- Contact check with microscope recommended

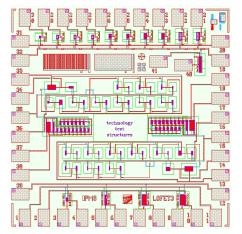

1 Layout of the Basic Logic Circuit with LOFET

# BASIC LOGIC CIRCUITS WITH LATERAL ORGANIC FIELD EFFECT TRANSISTORS (LOFET)

logic circuits. Here, up to 36 single transismaterials then only requires a frequency can be automated easily. This prevents the complicated and time-consuming measurement and analysis of the individual transistor characteristic. Furthermore, it is not only reliable information about logic capability that is acquired. The dynamic characteristics of the inverters are also determined.

The layout of a LOFET chip (Figure 1) includes an initial block with eleven individual transistors making a complete parameter extraction for circuit simulation possible. A second block contains four inverters which are replicated in the oscillators. These separately accessible inverter levels enable

One further step in simplifying materials a detailed analysis of the transient behavior characterization is the analysis of basic in case the amplification of the individual inverter stages is not sufficient for starting tors are interconnected to inverters and the oscillation of the ring oscillators. The ring oscillators. Monitoring of the active third block contains ring oscillators with either 7 or 15 stages. Each ring circuit has measurement of the ring oscillators which a three-stage output amplifier which decouples the oscillation inside the ring from the output terminal and allows a direct frequency measurement without external amplification. The LOFET substrates are also produced in bottom gate architecture so that functional circuits require the deposition of the semiconductor layer only.

#### PRODUCT PORTFOLIO

| characteristics                                                                               | bare OFET             | OFET Gen4,<br>90 nm SiO, | OFET Gen4,<br>230 nm SiO <sub>2</sub> | OFET Gen5             | OFET<br>AX1579        | OFET<br>AX1580        | OFET<br>AX1581        | Customized<br>OFET    | LOFET                 |

|-----------------------------------------------------------------------------------------------|-----------------------|--------------------------|---------------------------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| Wafer Substrate 150 mm<br>or 200 mm                                                           | •                     | •                        | •                                     | •                     | •                     | •                     | •                     | •                     | •                     |

| gate: n-doped silicon<br>(doping at wafer surface:<br>n~3e17 cm-3)                            | •                     | •                        | •                                     | •                     | •                     | •                     | •                     | •                     | 0                     |

| SiO <sub>2</sub> 90 nm                                                                        | 0                     | •                        | 0                                     | 0                     | 0                     | 0                     | 0                     | 0                     | 0                     |

| SiO <sub>2</sub> 200 nm                                                                       | 0                     | 0                        | 0                                     | 0                     | 0                     | 0                     | 0                     | 0                     | •                     |

| SiO <sub>2</sub> 230 nm                                                                       | •                     | 0                        | •                                     | •                     | •                     | •                     | •                     | 0                     | 0                     |

| SiO <sub>2</sub> thicknesses between<br>10 nm and 500 nm                                      | <b>0</b> <sup>1</sup> | <b>0</b> 1               | <b>0</b> 1                            | <b>9</b> <sup>1</sup> | <b>0</b> <sup>1</sup> | <b>9</b> <sup>1</sup> | <b>0</b> <sup>1</sup> | <b>9</b> <sup>1</sup> | 0                     |

| drain/source: 30 nm Au<br>with 10 nm ITO                                                      | 0                     | •                        | •                                     | •                     | •                     | •                     | •                     | •                     | 0                     |

| Design Gen 4:                                                                                 | 0                     | •                        | •                                     | 0                     | 0                     | •                     | •                     | 0                     | 0                     |

| 4 x transistors L=2.5 μm,<br>W=10 mm                                                          |                       |                          |                                       |                       |                       |                       |                       |                       |                       |

| 4 x transistors L=5 μm,<br>W=10 mm                                                            |                       |                          |                                       |                       |                       |                       |                       |                       |                       |

| 4 x transistors L=10 μm,<br>W=10 mm                                                           |                       |                          |                                       |                       |                       |                       |                       |                       |                       |

| 4 x transistors L=20 μm,<br>W=10 mm                                                           |                       |                          |                                       |                       |                       |                       |                       |                       |                       |

| Design Gen 5:                                                                                 |                       |                          |                                       |                       |                       |                       |                       |                       |                       |

| 4 x transistors L=2.5 μm,<br>W=2 mm                                                           |                       |                          |                                       |                       |                       |                       |                       |                       |                       |

| 4 x transistors L=5 μm,<br>W=2 mm                                                             | 0                     | 0                        | 0                                     | •                     | 0                     | 0                     | 0                     | 0                     | 0                     |

| 4 x transistors L=10 μm,<br>W=2 mm                                                            |                       |                          |                                       |                       |                       |                       |                       |                       |                       |

| 4 x transistors L=20 μm,<br>W=2 mm                                                            |                       |                          |                                       |                       |                       |                       |                       |                       |                       |

| Design AX1579:                                                                                |                       |                          |                                       |                       |                       |                       |                       |                       |                       |

| 4 x transistors L=10 μm,<br>W=2 mm                                                            |                       |                          |                                       |                       |                       |                       |                       |                       |                       |

| 4 x transistors L=20 μm,<br>W=2 mm                                                            | 0                     | 0                        | 0                                     | 0                     | •                     | 0                     | 0                     | 0                     | 0                     |

| 4 x transistors L=40 μm,<br>W=2 mm                                                            |                       |                          |                                       |                       |                       |                       |                       |                       |                       |

| 4 x transistors L=80 μm,<br>W=2 mm                                                            |                       |                          |                                       |                       |                       |                       |                       |                       |                       |

| Easy access to bondpads                                                                       | 0                     | 0                        | 0                                     | 0                     | 0                     | •                     | 0                     | <b>O</b> <sup>3</sup> | 0                     |

| Heater                                                                                        | 0                     | 0                        | 0                                     | 0                     | 0                     | 0                     | •                     | <b>0</b> <sup>3</sup> | 0                     |

| Source/drain layer: Ti/<br>TiN, Rs about 10 Ω/sq.<br>with 30nm Au with<br>10 nm ITO top layer | 0                     | 0                        | 0                                     | 0                     | 0                     | 0                     | 0                     | 0                     | •                     |

| Design:                                                                                       |                       |                          |                                       |                       |                       |                       |                       |                       |                       |

| transistors, inverters and ring oscillators                                                   | 0                     | 0                        | 0                                     | 0                     | 0                     | 0                     | 0                     | 0                     | •                     |

| Customized design                                                                             |                       |                          |                                       |                       |                       |                       |                       | •                     |                       |

| Compatibility OFET prober                                                                     | 0                     | •                        | •                                     | •                     | •                     | 0                     | <b>O</b> <sup>2</sup> | <b>0</b> <sup>3</sup> | 0                     |

| Package: waffle pack<br>(16 chips)                                                            | <b>0</b> 1            | •<br>Part 2028           | •<br>Part 1897                        | <b>0</b> 1            | ●<br>Part 2035        | •<br>Part 2036        | •<br>Part 2037        | •                     | <b>0</b> <sup>1</sup> |

| Package: diced on foil<br>(60 chips)                                                          | ●<br>Part 176         | 0                        | 0                                     | •<br>Part 175         | •<br>Part 2029        | •<br>Part 2030        | •<br>Part 2031        | <b>0</b> <sup>3</sup> | •<br>Part 267         |

| Package: diced on foil<br>(112 chips)                                                         | <b>O</b> <sup>1</sup> | •<br>Part 2017           | •<br>Part 1301                        | 0                     | 0                     | 0                     | 0                     | <b>1</b> 3            | 0                     |

- Feature not existing

- Feature existing

- Feature partly existing (see restrictions)

- <sup>1</sup> Available on request

- <sup>2</sup> Measurement works with OFET prober

- $^{\scriptscriptstyle 3}$  Depending on customer design