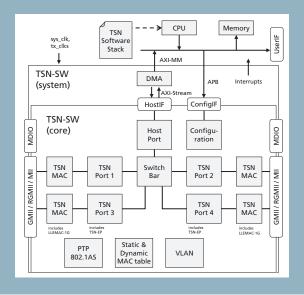

Time-Sensitive Networking (TSN) is a set of sub-standards that enhance the existing Ethernet specification towards time synchronization and deterministic communication in switched networks according to existing IEEE 802.1 and 802.3 standards. The goal is it to make Ethernet more suitable for the advancing needs of industrial, automotive and other applications. The TSN-SW is suitable for multiport switches with or without integrated endpoint functionality. A configurable number of 2 to 24 full-duplex Ethernet ports plus one internal port are available. The design implements a 1GbE switching bar with cut-through capability at wire speed. It provides time-sensitive networking for full-duplex point-to-point Ethernet communication.

Several hundreds of customers worldwide have relied on the quality of Fraunhofer IPMS IP-Core solutions for FPGA and ASIC designs and the comprehensive technical support for over 20 years.

#### **Applications**

The TSN-SW IP Core is suitable for the implementation of talkers and listeners within TSN Ethernet networks. The TSN-SW IP can be utilized for embedding real-time TSN applications into regular Ethernet networks. It is targeting for applications in industrial automation, robotics, automotive, aerospace and more.

Featuring a configurable number of ports, the Layer-2 switch operates in cut-through mode at wire speed and can provide sub-microsecond port-to-port latency. The core is hence suitable for applications with demanding real-time requirements.

# Verification

Interoperability of sub-modules is constantly tested within TSN plug-fests by LNI4.0 and Industrial Internet Consortium (IIC).

## Contact

Monika Beck +49 351 88 23 - 274 monika.beck@ipms.fraunhofer.de

Dr. Frank Deicke +49 351 88 23 - 385 frank.deicke@ipms.fraunhofer.de

Fraunhofer Institute for Photonic Microsystems IPMS Maria-Reiche-Str. 2 01109 Dresden Germany

www.ipms.fraunhofer.de

Schematic diagram of the TSN-SW IP Core.

#### **TSN Features**

- Time synchronisation (IEEE 802.1 AS-2020)

- Traffic-Shaping (IEEE 802.1 Qav and Qbv)

- Frame Preemption (IEEE 802.3br and IEEE 802.1Qbu)

- Frame Replication and Elimination (IEEE 802.1CB)

- SRP Enhancements (IEEE 802.1Qcc)

- Stream Filtering and Policing (IEEE 802.1Qci)

- Ethernet MAC communication (IEEE 802.3)

- 802.1Q Tagged VLAN support

- Configurable VLAN-PCP to TSN-Queue Mapping (QoS by PCP)

- IPMS AXI4-DMA core optional

#### **Easy Integration**

- Platform independent implementation into any FPGA or foundry technology

- TSN-SW IP core can be attached to custom SoC or a complete TSN-SW can be provided

- Intel Altera based evaluation platform

- Xilinx based evaluation platform

- Set of demo projects for Xilinx and Intel Altera

- Configurable feature set

- Responsive support

- TSN Evaluation Kit available

## **IEEE 802.1Q Switch Features**

- Low-latency Layer 2 switch cut-through switching at wire speed

- Configurable number of 2 to 24 full-duplex Ethernet ports plus one internal port

- Supports up to 1024 dynamic and static MAC table entries

- 8 Gbps Fwd-Bandwidth at 4 Ports

- Cut-through or store-and-forward TSN frame forwarding

- Ports run full-duplex at 10/100/1000 Ethernet

- PHY configuration via MDIO

- Port based 12bit VLAN-ID support

- Automatic ageing table support

- Statistics by widely configurable counters

#### **Deliverables**

- Verilog RTL source code or targeted FPGA netlist

- Testbenches

- Sample simulation and synthesis scripts

- Comprehensive documentation

- TSN FreeRTOS Unified Framework, CLI example, PTP-AS2020

- FreeRTOS example projects

- Linux driver reference design

### **Designed for Usage with Ethernet MACs**

- ALTERA/Intel Triple Speed Ethernet MAC

- XILINX Tri-Mode Ethernet MAC

- IPMS Triple Speed Low-Latency Ethernet MAC

- Triple speed: 10 / 100 / 1000 Mbit/s Ethernet

- 2.5/5/10+ Gbps on request

- Host Interfaces to AXI, AvalonST/MM

- PHY Interfaces to MII, GMII and RGMIII

- Memory-Mapped MDIO interface per port for PHY configuration

### **Data Interfaces**

- Advanced Peripheral Bus (APB) for memory mapped register access

- 32 bit AXI-Streams for TX data

- Avalon interfaces available

- More interfaces upon request

TSN Evaluation Kit: Xilinx ZCU102 or Intel Netleap (Cyclone V SoC); implemented IPMS TSN-IP core for switch applications (TSN-SW).