### FRAUNHOFER CENTER NANOELECTRONIC TECHNOLOGIES

# JAHRESBERICHT ANNUAL REPORT 2011

Preface

### Fraunhofer Center Nanoelectronic Technologies Ove

Profile

Figures

Cooperation

### **Competence Areas and Research Results**

Analytics

Functional Electronic Materials - Front End of Line

Functional Electronic Materials - Back End of Line

Maskless Lithography

Devices & Integration

Events

Publications

Contact

**Editorial Notes**

# CONTENTS

|         | 4  |

|---------|----|

| verview |    |

|         | 8  |

|         | 12 |

|         | 16 |

|         |    |

|         | 19 |

|         | 20 |

| 2       | 26 |

|         | 32 |

|         | 40 |

|         | 46 |

|         |    |

|         | 54 |

|         | 59 |

|         | 64 |

|         | 65 |

|         |    |

# PREFACE

Für das Fraunhofer Center Nanoelektronische Technologien (CNT) war 2011 ein erfolgreiches Jahr, in dem einige Rahmenbedingungen für die zukünftige Entwicklung geschaffen wurden.

Die lange Zeit der Ungewissheit seit 2009 bezüglich der angemieteten Reinraum-, Labor- und Büroflächen nach der Insolvenz des Industriepartners Qimonda, wurde mit dem Erwerb des ehemaligen Qimonda-Geländes durch Infineon im Juni 2011 beendet. Infineon hat das Interesse bekundet, die Flächen auch weiterhin an Fraunhofer zu vermieten und standortbezogene Dienstleistungen anzubieten. Die Verhandlungen dazu sollen in 2012 abgeschlossen werden. In einem umfassenden Strategieprozess haben wir langfristig die Kernkompetenzen und Geschäftsfelder neu definiert sowie die Ziele festgelegt. Der Jahresbericht gibt Ihnen dazu einen guten Überblick. Besonders erfreulich ist die Zunahme von Aufträgen, neben großen IC-Herstellern, gerade von mittelständischen Unternehmen und Start-up Firmen, die unabhängig von Förderprojekten direkt an die Einrichtung erteilt wurden und in diesem Jahr, den Umfang von nahezu einer Million Euro erreichten. Dies ist einmal mehr der Beweis für die Wertschätzung der vorhandenen Kompetenzen und die Erkenntnis, dass die Ergebnisse aus der Nanoelektronik zunehmend Anwendungen auch in Systemen der Mikroelektronik finden gemäß dem Motto "Nano for Micro". Mein besonderer Dank geht an die Auftraggeber, die das Fraunhofer CNT auch in den turbulenten vergangenen Jahren als zuverlässigen Forschungsdienstleister geschätzt haben, woraus sich auch einige längerfristige Partnerschaften entwickelten.

Als Beispiel sei hier ASM International genannt. Nach mehreren Jahren vertrauensvoller Zusammenarbeit konnte mit diesem international führenden Anlagenhersteller eine längerfristige, bilaterale Kooperation im Bereich Atomlagenabscheidung (ALD) und Epitaxie abgeschlossen werden. Unsere Kompetenz im Bereich Prozesse, 2011 was a successful year for Fraunhofer Center Nanoelectronic Technologies (CNT) in which the framework for future development has been created.

The long period of uncertainty since 2009 regarding the rented cleanroom, laboratory and office space followed by the insolvency of industry partner Qimonda, has been completed with the acquisition of Qimonda's properties by Infineon in June 2011. Infineon has expressed an interest in further collaborations with Fraunhofer by providing facilities and location-based services. The negotiations should be completed in 2012. Long-term core competencies, business areas and goals have been established in a comprehensive strategy process. This annual report gives you a good overview.

Particularly pleasing is the increase of orders, from major IC manufacturers and especially from mediumsized companies and start-up companies which were granted, regardless of funding projects, directly to the institution. This year, the amount has reached nearly one million Euros. This is another proof of the appreciation of the CNT competencies and the evidence that results from nanoelectronic research increasingly find applications in microelectronics systems in accordance with the slogan "Nano for Micro."

My special thanks goes to the authorities who have valued the Fraunhofer CNT as reliable research service provider in the turbulent last years from which, also some longer-term partnerships have developed. As an example, ASM International is mentioned. After several years of faithful cooperation with this leading international equipment manufacturer, a longer-term bilateral cooperation in the field of atomic layer deposition (ALD) and epitaxy is completed. Our expertise in processes, materials and equipment is planned to be expanded through further cooperation. Materialien und Anlagen soll zukünftig durch weitere Kooperationen ausgebaut werden. Als ein beständiger Partner für Entwicklungsprojekte erwies sich unser Industriepartner GLOBALFOUNDRIES. Durch dessen deutliche Verbreiterung des Technologie- und Produktportfolios als Foundry ergaben sich zusätzliche Anknüpfungspunkte für Industrieaufträge, die erfolgreich zum Abschluss gebracht wurden. Zudem sind neue Forschungsinhalte definiert worden. Mehrere Projekte und Vereinbarungen konnten zudem mit anderen IC-Herstellern, IP-Firmen und Anlagenherstellern sowohl im Bereich Abscheidung, Hoch-Temperatur Behandlung als auch bei Testsystemen z.B. mit der Firma Tokyo Elektron (TEL) getroffen werden. Seit Mitte 2011 konnte das Fraunhofer CNT auf eine Grundfinanzierung zurückgreifen. Damit wurden unter anderem die vorhandenen Kompetenzen für MIM (Metall-Isolator-Metall) Kondensatorstrukturen, z.B. für Pufferspeicher in Analog/Digital Mixed Signal Bausteinen oder in mikroelektronischen Systemen, weiterentwickelt.

Durch die vom Land Sachsen geförderten Projekte in den Geschäftsfeldern "Enabling 300mm Production" und "Nanopatterning" sowie "Innovative Materialien und Prozesse für die Nano-und Mikroelektronik" konnte die herausragende Qualität und das Potential der etablierten Technologien gerade in der breiten Anwendung für die Mikrosystemtechnik und Nanoelektronik bei Strukturen unter 30 nm demonstriert werden. Durch diese Projekte hat die Einrichtung wesentlich dazu beitragen, Innovationen in den "Key Enabling Technologies" voranzutreiben, wie in einer EU Kommunikation im September 2009 "Preparing for our future: Developing a common strategy for key enabling technologies in the EU"{SEC(2009) 1257} beschrieben.

Damit liefert das Fraunhofer CNT auch weiterhin einen<br/>wesentlichen Beitrag für die herausragende Stellunga link between "More Moore" and "More than Moore"<br/>technologies and applications.Dresdens als Mikroelektronik-Standort in Europa, als<br/>Bindeglied zwischen "More Moore" und "More than<br/>Moore" Technologien und Anwendungen. BesondersParticularly encouraging, the conclusion of two other<br/>promotions at Fraunhofer CNT with the subjects:

A steady partner for development projects is our industry partners GLOBALFOUNDRIES. Its significant broadening of the technology and product portfolio as a foundry resulted in additional industry orders that have been completed successfully. In addition, new research content has been defined. Several projects and agreements were also made with other IC manufacturers, IP companies and equipment manufacturers in the field of deposition, high-temperature treatment as well as in test systems with the company Tokyo Electron (TEL).

Since mid-2011, Fraunhofer CNT can rely on core funding. Among other things, this was used to develop the existing competencies for MIM (metal-insulatormetal) capacitor structures, e.g. for buffer memory in analog / digital mixed signal ICs or in microelectronic systems evolved.

By the state of Saxony-funded projects in the fields of "enabling 300mm Production" and "Nanopatterning" and "Innovative materials and processes for nano-and microelectronics" the outstanding quality and the potential of established technologies currently in wide use for microsystems technology and nanoelectronics were demonstrated in structures below 30 nm.

Through these projects, the Fraunhofer CNT was able to significantly push innovations in the "Key Enabling Technologies" forward, stated in an EU Communication in September 2009 "Preparing for our future: Developing a common strategy for key enabling technologies in the EU" {SEC (2009 ) 1257}.For this reason the Fraunhofer CNT continues to contribute to the prominent position of Dresden as a microelectronic location in Europe, as a link between "More Moore" and "More than Moore" technologies and applications.

# PREFACE

erfreulich war auch der Abschluss von zwei weiteren Promotionen im Fraunhofer CNT mit den Themen: Kinetik der elektrochemischen Kupferabscheidung in Sub-100 nm-Strukturen und der Analyse von High-k Materialien mittels Atom Probe. Alle Doktoranden bestätigten die Effektivität mit der die Arbeiten, gerade durch die enge Zusammenarbeit mit der Industrie und den betreuenden Professoren, durchgeführt werden konnten. Viele Mitarbeiter und Mitarbeiterinnen haben sich im Laufe des Jahres z.B. bei der "Langen Nacht der Wissenschaften" oder beim Praktikum von Schülern, z.B. des Martin-Andersen-Nexö Gymnasiums engagiert.

Am 2. November fand der zweite "Fraunhofer CNT Research Day" statt. Dafür konnten wir mehrere Experten mit Beiträgen von führenden Unternehmen wie z.B. Infineon, STMicroelectronics, ASM und CEA-Leti, Air Liquide begrüßen, die neben Wissenschaftlern aus unserem Institut neueste Erkenntnisse und Strategien auf verschiedenen Fachgebieten vorstellten. Die große Beteiligung mit nahezu 100 Teilnehmern und das positive Feedback der Gäste sind Motivation, diese Veranstaltung auch im nächsten Jahr fortzuführen. Als Auszeichnung für die wissenschaftliche Kompetenz am CNT dürfen wir die Entscheidung werten, den 17th Workshop on Dielectrics in Microelectronics (WoDiM) vom 25.- 27.6.2012 ausrichten zu dürfen.

Die Einrichtung wurde mit ihren Kompetenzbereichen und der Ausrichtung auf neue Anwendungsfelder optimiert aufgestellt. Für das Jahr 2012 und darüber hinaus ermöglicht dies ein weiteres Wachstum und lässt uns positiv in die Zukunft schauen. Dies verdankt das Fraunhofer CNT engagierten und kompetenten Mitarbeitern und Mitarbeiterinnen sowie unseren Partnern aus der Industrie, anderen Forschungseinrichtungen und Instituten, denen ich an dieser Stelle besonders für das entgegengebrachte Vertrauen danken möchte. kinetics of electrochemical deposition of copper in sub-100 nm structures and the analysis of high-k materials with Atom Probe. All students confirmed the effectiveness of their work through a close cooperation with the industry and the supervising professors. Many staff members were engaged in activities such as the "Night of Science" or the internship of students e.g. from the "Martin Andersen Nexo"-school.

On November 2nd the second "Fraunhofer CNT Research Day" took place with several experts from leading companies such as Infineon, STMicroelectronics, ASM and CEA-Leti, Air Liquide and researchers from our institute who presented the latest results and strategies in various fields. The large turnout with about 100 participants and the positive feedback from guests are motivation to continue this event again in 2012. As recognition of the scientific expertise at the CNT, we evaluate the decision, to host the 17th Workshop on Dielectrics in Microelectronics (WoDiM) June 25 - 27, 2012 in Dresden.

The facility has been optimized regarding its competence areas and new fields of applications. For the year 2012 and beyond, this allows further growth and a positive perspective for the future. I would like to use this opportunity to thank our highly motivated and competent employees as well as all our business partners and supporters for their confidence.

der hüchen

Prof. Dr. Peter Kücher

# PROFILE

### Forschung und Entwicklung im Fraunhofer CNT

Das Geschäftsfeld des Fraunhofer CNT umfasst die Entwicklung von Prozessschritten und Materialien sowie die physikalische und elektrische Charakterisierung für High-Performance-Logik, Derivate (z. B. embedded DRAM) und Speichertechnologien für flüchtige und nicht-flüchtige Bauelemente.

Zielsetzung der Einrichtung ist es, innovative Einzelprozesslösungen für nanoelektronische Systeme vor allem auf 300 mm Wafern mit Industriepartnern und anderen Forschungseinrichtungen so zu entwickeln, dass diese schnell in ein industrielles Fertigungsumfeld übertragen werden können.

Das Leistungsangebot des Fraunhofer CNT basiert auf fünf Kompetenzbereichen:

- Analytik

- Funktionale Elektronische Materialien Front End of Line

- Funktionale Elektronische Materialien Back End of Line

- Devices & Integration

- Maskenlose Lithographie

Die Kompetenzbereiche forschen vor allem in den folgenden Geschäftsfeldern:

- Leading Edge Technologie f

ür die Nano-Mikroelekt ronik

- Enabling 300 mm Production

- Nanostructuring

# Research and Development at Fraunhofer CNT

The business areas of Fraunhofer CNT include the development of processes and materials as well as the physical and electrical characterization of high-performancelogics, derivates (e. g. embedded DRAM) and memory technologies for volatile and non-volatile devices.

In close cooperation with industrial partners and other R&D organizations, the objective of our institute is to develop innovative unit process solutions for nanoelectronic systems on 300 mm silicon wafers. The aim is to transfer research results fast into industrial manufacturing.

The range of services offered by Fraunhofer CNT is based on five competence areas:

- Analytics

- Functional Electronic Materials Front End of Line

- Functional Electronic Materials Back End of Line

- Devices & Integration

- Maskless Lithography

The competence areas do research especially in the following fields:

- Leading edge technology for nano-micro-electronic

- Enabling 300 mm production

- Nanostructuring

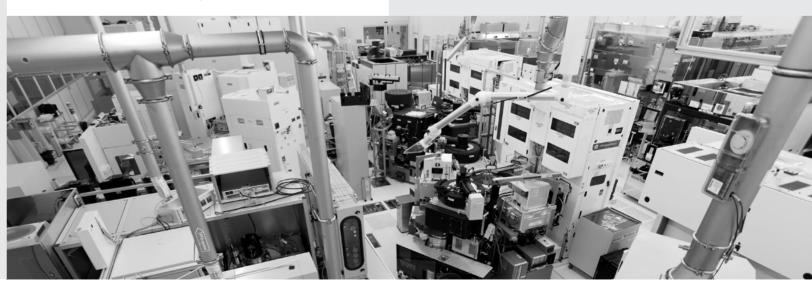

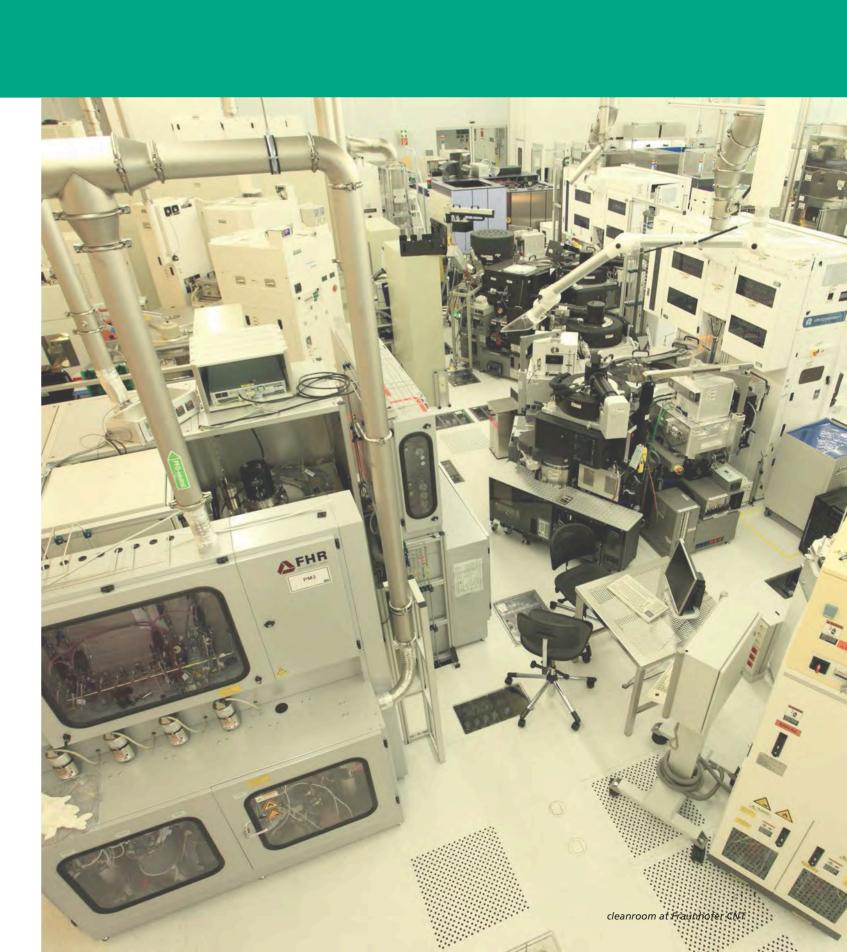

### Ausstattung

Für das Fraunhofer CNT stehen derzeit 800 m² Reinraum-<br/>fläche (Reinraumklasse 1000) sowie eine Infrastruktur zur<br/>Verfügung, die dem Industriestandard entspricht. Zusätzlich<br/>zu den ca. 40 Anlagen im Reinraum können umfangreiche<br/>Analyse- und Metrologieverfahren für die Forschung und<br/>Entwicklung sowie die Bausteincharakterisierung genutztAt present, Fraunhofer CNT uses 800 m² clean room<br/>area (class 1000) and an infrastructure which meets<br/>industry standards. In addition to 40 clean room tools,<br/>scientists at Fraunhofer CNT use considerable analytical<br/>and metrological processes for R&D as well as for the<br/>characterization of nanoelectronic devices.

Die Einrichtung unterhält keine durchgängige ProzesslinieThe institute does not maintain a continuous processin der alle notwendigen Prozessschritte zur Realisierung<br/>höchstintegrierter Chips zur Verfügung stehen. Sie verfügt<br/>aber über neue, fertigungstypische Prozessgeräte, an<br/>denen die Partner zusammen mit den Wissenschaftlern im<br/>Fraunhofer CNT forschen und entwickeln können.The institute does not maintain a continuous process<br/>line to cover all the necessary process steps in order<br/>to realize high-integrated memory chips. However,<br/>Fraunhofer CNT possesses new process tools which are<br/>typical of production and enabling common research<br/>and development with its partners.

Teilprozessierte Wafer kommen von GLOBALFOUNDRIES -<br/>die innovativen Prozessschritte werden im Fraunhofer CNT<br/>durchgeführt. Die gewonnenen Erkenntnisse können dann<br/>sofort in die praktische Erprobung in der angrenzenden<br/>Fertigung übertragen werden. Dadurch lassen sich sowohlPre-processed wafers are provided by GLOBALFOUNDRIES<br/>– innovative process steps will be operated at Fraunhofer<br/>CNT. Thus, the results can be transferred immediately<br/>into manufacturing. This enables partners to reduce<br/>their capital expenditures. Moreover, it allows a faster<br/>schedule.Schnellerer Zeitablauf ermöglichen.schedule.

### Environment

# PROFILE

# **COLLABORATION**

### **Kooperationspartner in unmittelbarer** Umgebung

Das Fraunhofer-Center Nanoelektronische Technologien - 2005 entsprechend dem Modell einer Public-Private-Partnership gegründet - ist neben der erfolgreichen Kooperation mit dem Halbleiterhersteller GLOBALFOUNDRIES Dresden Module One LLC & Co. KG auch für die Zusammenarbeit und Durchführung von Projekten mit verschiedenen Forschungseinrichtungen, Industriepartnern und Universitäten sowie Zulieferfirmen der IC-Industrie wie Material- und Geräteherstellern offen.

In unmittelbarer Umgebung des Fraunhofer CNT befinden sich die Halbleiterhersteller GLOBALFOUNDRIES, Infineon und X-Fab. Dazu bietet Dresden, eingebettet in Silicon Saxony, ausgezeichnete Standortbedingungen für das Fraunhofer CNT als etablierte Forschungsplattform der Nanoelektronik. Durch die lokale Nähe zu den Fertigungslinien des Partners und das vorhandene Know-how können viele Synergieeffekte genutzt werden. Dadurch ist es möglich, Entwicklungen und neue Prozesse schnell in die Fertigungsabläufe einzubauen, was es wiederum erlaubt Herstellungskosten und -zeit zu sparen.

"Durch die Nutzung von Synergien zwischen der Referenz von Fertigungslinien, basierend auf modernster 300 mm Wafertechnologie, sowie dem Fachwissen unserer Mitarbeiter können wir Projekte erfolgreich und zeitnah durchführen."

Prof. Dr. Peter Kücher

### **Cooperation partner in the immediate** vicinity

Fraunhofer Center Nanoelectronic Technologies was founded in 2005 according to the model of a public private partnership. A part from the successful cooperation with the semiconductor manufacturer GLOBALFOUNDRIES Dresden Module One LLC & Co. KG, the institute is open for the collaboration and execution of projects with different research organizations, industrial partners, universities as well as semiconductor suppliers such as material and tool manufacturers.

The semiconductor manufacturers GLOBALFOUNDRIES, Infineon and X-Fab are located close to Fraunhofer CNT. In addition, Dresden and Silicon Saxony offer excellent site conditions. Because of the proximity to the manufacturing lines of the partners and of the established know-how, Fraunhofer CNT benefits from numerous synergy effects. Thus, it is possible to implement innovative developments and new processes fast into manufacturing. It also enables the partners to save time and production costs.

"Benefiting from synergies between the reference of the manufacturing lines on the basis of latest 300 mm wafer technology as well as of the know-how of our employees, we are able to perform our projects successfully and immediately."

Prof. Dr. Peter Kücher

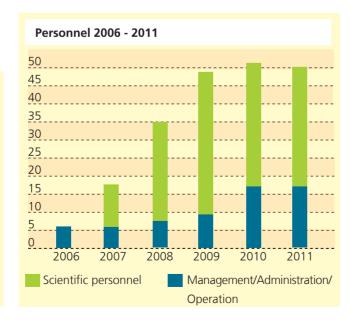

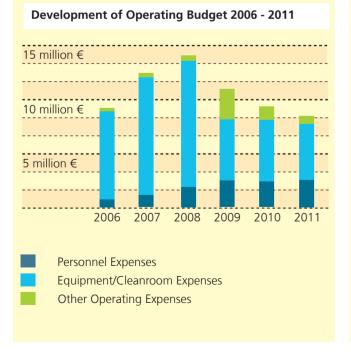

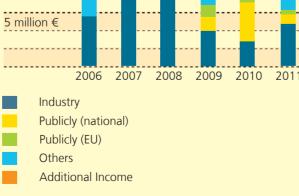

# **FRAUNHOFER CNT IN FIGURES**

Das Fraunhofer CNT erwirtschaftete 2011 einen Ertrag von ca. 8,8 Mio Euro. Der Betriebshaushalt setzte sich zu ca. 51 % aus Wirtschaftserträgen, zu etwa 7 % aus Erträgen aus nationalen öffentlichen Projekten, zu rund 3 % aus EU-Erträgen, zu rund 22 % aus sonstigen Erträgen und zu 17 % aus Sonderfinanzierungsmitteln zusammen.

Zur Bearbeitung der Forschungsaufträge stehen auf 800 m<sup>2</sup> Reinraumfläche und 200 m<sup>2</sup> Laborfläche modernste Laborausstattungen und Großgeräte zur Verfügung. Der Anlagenpark umfasst Abscheide- und Ätzanlagen für die Wärmebehandlung bei Hochtemperaturen sowie Inspektions- und Analysegeräte zum Bestimmen von Defekten und dem Messen von Schichteigenschaften.

Zum Jahresende 2011 beschäftigte das Fraunhofer CNT 49 festangestellte Mitarbeiter. Das Personal setzte sich aus 32 Wissenschaftlern einschließlich 7 Doktoranden, 6 technischen Mitarbeitern und 11 Mitarbeitern in Management und Verwaltung zusammen. Mit modernstem Anlagenpark, intensiver Vorlaufforschung sowie einer langjährigen Industrieerfahrung stehen die Mitarbeiter des Fraunhofer CNT ihren nationalen und internationalen Kunden und Partnern zur Seite, um Innovationen für die Zukunft nutzbar zu machen.

| Annual Budget 2011 in k € in % |       |     |  |  |  |  |

|--------------------------------|-------|-----|--|--|--|--|

| Revenues                       | 8.771 |     |  |  |  |  |

| Industry                       | 4.508 |     |  |  |  |  |

| Publicity (national)           |       | 7,0 |  |  |  |  |

|                                | 281   |     |  |  |  |  |

| Others                         |       |     |  |  |  |  |

|                                | 1.432 |     |  |  |  |  |

In 2011 Fraunhofer CNT generated revenues of about 8.8 million Euro. The operation budget was composed of 51 % of industry returns, 3 % earnings from national public projects, 7 % of EU earnings, 22 % of other revenues and 17 % of special financing.

In order to process R&D wafers professionally, Fraunhofer CNT has an area of 800 m<sup>2</sup> clean room and 200 m<sup>2</sup> laboratory available which are equipped with the latest semiconductor R&D tools. The equipment ranges from deposition and etching tools used for the heat treatment at high-temperatures as well as from inspection and analytic tools which are used for the characterization of defects and layers.

In the end of 2011, Fraunhofer CNT employed 49 permanent staff. The personnel was composed of 32 scientists including 7 Ph.D. students, 6 technicians and 11 employees in administration and management. Equipped with the latest devices, intense initial research and a long-lasting industry know-how, employees of Fraunhofer CNT provide support to their national and international customers and partners in order to realize innovations in the future.

Das Fraunhofer CNT hat 2011 ca. 1 Mio Euro investiert, um sein technisches Equipment zu erweitern. Diese Investitionen wurden aus dem Europäischen Fond für Regionale Entwicklung und vom Freistaat Sachsen gefördert sowie aus Sondermitteln finanziert.

Der strategische Industriepartner Globalfoundries setzte seine Zusammenarbeit mit dem Fraunhofer CNT kontinuierlich in mehrere bereits vor 2011 gestarteten Forschungsvorhaben fort.

Für Globalfoundries wurde so beispielsweise eine schädigungsfreie, plasmagestützte Strukturierung von Ultra-low-k Dielektrika für die Anwendung in einer sub30nm-Technologie entwickelt.

Ein weiteres Projekt beinhaltet die **Entwicklung zukünftiger High-k Gate-Dielektrik-Transistoren** einschließlich einer Machbarkeitsstudie für ferroelektrische Speicher.

Darüber hinaus arbeiteten die Wissenschaftler des CNT in einem Projekt an der **Entwicklung einer Verdrahtungstechnologie für kleinste Strukturen** unter Berücksichtigung der wachsenden Anforderungen an die elektrische Zuverlässigkeit, sowie in einem Projekt an der **Optimierung von Metal-Gate-Prozessen** für die Replacement-Gate-Technologie und Entwicklung von Prozessen zur Verbesserung der Zuverlässigkeit von High-k-Metal-Gate (HKMG)-Stapeln.

Das in 2010 von Globalfoundries beauftragte Projekt "Verbesserung der Mikroprozessoreneigenschaften mittels Einsatz von Kohlenstoff" wurde in 2011 erfolgreich abgeschlossen.

Weitere Projekte wurden mit verschiedenen namhaften Forschungseinrichtungen und Unternehmen umgesetzt, so beispielsweise ein Projekt mit ASELTA Nanographics (Frankreich) zur E-Beam Proximity Effekt Korrektur für die Herstellung von optischen Masken und Anwendungen im Bereich der maskenlosen Lithografie.

The Fraunhofer CNT has invested about € 1 million to expand its technical equipment in 2011. These investments were financed through the European Regional Development Fund, the Free State of Saxony and from special funds.

The strategic industry partner Globalfoundries steadily continued his collaboration with the Fraunhofer CNT in several research projects that started before 2011.

One development for Globalfoundries was a damagefree, plasma-based patterning of ultra-low-k dielectrics for the use in a sub30nm technology. Another project involves the **development of future high-k gate dielectric transistors** including a feasibility study for ferroelectric memory.

Furthermore, scientists at CNT were working on a project to **develop a wiring technology for smallest structures**, considering the growing demands on the electrical reliability. Another project is working on the **optimization of metal-gate processes for the replacement-gate** technology and development of processes to improve the reliability of high-k metal gate (HKMG) stacks.

The in 2010 commissioned Globalfoundries project "Improvement of the microprocessor features through the use of carbon" was successfully completed in 2011.

Other projects have been implemented with several renowned research institutes and companies, such as the project with ASELTA Nano Graphics (France) for e-beam proximity effect correction for the manufacture of optical masks and applications in maskless lithography.

Zusammen mit der Namlab gGmbH entwickelte das Fraunhofer CNT **ALD-Abscheidetechniken** für Hafnumdioxid basierende neue Materialien und wenige atomlagendicke Schichtsysteme.

Im Rahmen des Spitzenclusters CoolSilicon ist das Fraunhofer CNT an dem Teilvorhaben "Technologien für energieeffiziente Computing-Plattformen" beteiligt und untersucht hier einen selektiven SiGe-Epitaxieprozess mit insiut-Dotierung.

Im Bereich Analytik erprobt das Fraunhofer CNT im Rahmen eines sächsischen Verbundprojektes gemeinsam mit der Firma X-FAB Silicon Foundries innovative Analyseverfahren für die Optimierung von Fertigungsprozessen bei der Herstellung von mikroelektronischen Bauelementen mittels 3D-Atomsonde, HR-TEM und SIMS. Together with the NaMLab gGmbH, the Fraunhofer CNT developed **ALD deposition techniques** for Hafnumdioxid based new materials and a few atomic layer thick-layer systems.

As part of the Excellence Cluster "Cool Silicon" Fraunhofer CNT is involved in the sub-project "Technologies for Energy Efficient Computing Platforms" and is investigating a selective SiGe epitaxy with insiut doping.

As part of a joint Saxon project, Fraunhofer CNT and X-FAB Silicon Foundries testing innovative analytical methods for the optimization of manufacturing processes in the manufacture of microelectronic devices using 3D atom probe, HR-TEM and SIMS.

# **INNOVATION THROUGH COOPERATION**

### FRAUNHOFER-GESELLSCHAFT

Forschen für die Praxis ist die zentrale Aufgabe der Fraunhofer-Gesellschaft. Die 1949 gegründete Forschungsorganisation betreibt anwendungsorientierte Forschung zum Nutzen der Wirtschaft und zum Vorteil der Gesellschaft. Vertragspartner und Auftraggeber sind Industrie- und Dienstleistungsunternehmen sowie die öffentliche Hand.

Die Fraunhofer-Gesellschaft betreibt in Deutschland derzeit mehr als 80 Forschungseinrichtungen, davon 60 Institute. Mehr als 17.000 Mitarbeiterinnen und Mitarbeiter, überwiegend mit natur- oder ingenieurwissenschaftlicher Ausbildung, bearbeiten das jährliche Forschungsvolumen von 1,7 Mrd Euro. Davon fallen 1,4 Mrd Euro auf den Leistungsbereich Vertragsforschung. Zwei Drittel dieses Leistungsbereichs erwirtschaftet die Fraunhofer-Gesellschaft mit Aufträgen aus der Industrie und mit öffentlich finanzierten Forschungsprojekten. Nur etwas ein Drittel wird von Bund und Ländern als Grundfinanzierung beigesteuert, damit die Institute Problemlösungen erarbeiten können, die erst in fünf oder zehn Jahren für Wirtschaft und Gesellschaft aktuell werden.

### FRAUNHOFER IN DRESDEN: **GEBALLTE FORSCHUNG**

Die Fraunhofer-Gesellschaft ist mit sechs Instituten und sechs weiteren Einrichtungen in Dresden vertreten. Die zwölf Fraunhofer-Einrichtungen beschäftigen zusammen mehr als 1.100 Mitarbeiter bei einem jährlichen Umsatz von über 100 Mio Euro. Für die nächsten Jahre wird ein weiteres Wachstum prognostiziert.

Neben der außerordentlich hohen Dichte an Forschungseinrichtungen zeichnet sich der Standort Dresden durch eine enge Verflechtung von Industrie und Forschung aus. Die daraus entstehenden Spitzenleistungen und innovativen Entwicklungen setzen weltweite Impulse.

### **FRAUNHOFER-GESELLSCHAFT**

Research for practice is the main issue of all activities pursued by the Fraunhofer-Gesellschaft. The research organization, which was founded in 1949, undertakes applied research that drives economic development and serves the wider benefit of society. Its services are solicited by customers and contractual partners in industry, the service sector and public administration.

At present, the Fraunhofer-Gesellschaft maintains more than 80 research units in Germany, including 60 Fraunhofer institutes. The majority of the more than 17.000 employees are gualified scientists and engineers who work with an annual research budget of 1.7 billion euro. More than 1.4 billion euro of this amount are generated through contract research. Two thirds of the Fraunhofer-Gesellschaft's contract research revenues derive from contracts with industrial partners and from publicly financed research projects. Only one third is contributed by the German federal and Länder governments in the form of base funding which enables the institutes to work ahead on solutions to problems that will become relevant to industry and society in five or ten years.

### FRAUNHOFER IN DRESDEN: **CLUSTERED RESEARCH**

The Fraunhofer-Gesellschaft is represented in Dresden by six institutes and six other facilities. More than 1.100 employees work for the twelve Fraunhofer facilities. The annual turnover amounts to more than 100 million euro and further growth is expected within the next years.

In addition to the extraordinarily high density of research facilities, the region is characterized by the close connection between research and industry, resulting in the creation of leading-edge services and innovative developments which have a global impact.

# FRAUNHOFER VERBUND MIKROELEKTRONIK FRAUNHOFER GROUP MICROELECTRONICS

Der Fraunhofer-Verbund Mikroelektronik (VµE) koordiniert die Aktivitäten der auf den Gebieten Mikroelektronik und Mikrointegration tätigen Fraunhofer-Institute.

Technologiekompetenz des Verbunds reicht von The group's expertise ranges from classic CMOS technology Die klassischen CMOS-Technologie bis zum Einsatz to the use of innovative system solutions. Apart from der innovativer Systemlösungen. Sie schließt neben Silizium silicon, this also includes compound semiconductors and auch Verbindungshalbleiter und neue Materialien ein. Die new materials. Expertise in developing CMOS and other Kompetenz in der Entwicklung von CMOS- und anderen device technologies for microelectronics forms the basis Bauelementetechnologien für die Mikroelektronik stellt die for both, technological services and application-specific Basis sowohl für technologische Dienstleistungen als auch für component development. Fraunhofer CNT is the contact anwendungsbezogene Komponentenentwicklung dar. Das for the business area Technology which consists of two Fraunhofer CNT ist Ansprechpartner für die Bereiche "More divisions: "More Moore" and "Beyond CMOS" Moore" und "Beyond CMOS" im Geschäftsfeld Technologie

### The Fraunhofer Group for Microelectronics (VµE) coordinates the activities of Fraunhofer institutes working in the fields of microelectronics and microintegration.

Angewandte Festkörperphysik IAF Elektronische Nanosysteme ENAS Hochfrequenzphysik und Radartechnik FHR Integrierte Schaltungen IIS Integrierte Systeme und Bauelementetechnologie IISB Mikroelektronische Schaltungen und Systeme IMS Modulare Festkörper-Technologien EMFT Nachrichtentechnik, Heinrich-Hertz-Institut HHI Nanoelektronische Technologien CNT Photonische Mikrosysteme IPMS Siliziumtechnologie ISIT Systeme der Kommunikationstechnik ESK Zuverlässigkeit und Mikrointegration IZM

Gastinstitute / Guest Institutes Digitale Medientechnologie IDMT Offene Kommunikationssysteme FOKUS Zerstörungsfreie Prüfverfahren IZFP

# **INNOVATION THROUGH** COOPERATION

### **CLUSTER NANOANALYTIK**

Seit Oktober 2009 ist das Fraunhofer CNT Mitglied im Dresdner Fraunhofer-Cluster Nanoanalytik. Zehn Fraunhofer-Institute und drei Fakultäten der Technischen Universität Dresden sowie das Helmholtz-Zentrum Berlin bündeln ihre Kompetenzen und decken das gesamte Themenspektrum der Nanoanalytik ab. Die Institute sind flexibel vernetzt und werden auch sehr umfassenden Anforderungen im Bereich Analytik gerecht.

### **ALD LAB DRESDEN**

Im Oktober 2010 wurde das ALD Lab Dresden gegründet. Mit dem Lab werden Kompetenzen auf dem Gebiet der ALD (Atomlagenabscheidung) am Standort Dresden, dem Institut für Halbleiter- und Mikrosystemtechnik (IHM) der Technischen Universität Dresden (Prof. Johann Bartha) und der ALD-Gruppe des Fraunhofer CNT (Dr. Jonas Sundqvist) zusammengeführt. Gemeinsam entwickeln die Partner neue ALD-Precursoren und -Prozesse für die Halbleiter- und Photovoltaik-Industrie

### **E-BEAM-INITIATIVE**

Seit April 2010 ist das Fraunhofer CNT offizielles Mitglied der E-Beam-Initiative.

Die Initiative bietet ein Forum für bildungs- und verkaufsfördernde Aktivitäten, unter dem Gesichtspunkt eines neuen "design-to-manufacturing"-Ansatzes, bekannt als "design for e-beam" (DFEB). DFEB reduziert Maskenkosten für Halbleiterbauelemente, in Verbindung mit Design, Design-Software, Herstellung, Herstellungsmaterialien und Hersteller-Software-Expertise.

### **CLUSTER NANOANALYTIK**

Since October 2009, Fraunhofer CNT has been a member of the Fraunhofer-Cluster Nanoanalytics in Dresden. Ten Fraunhofer institutes, three faculties of the Dresden University of Technology as well as the Helmholtz-Zentrum Berlin consolidate their competences and thus cover the entire field of nanoanalytics. The institutes are flexibly linked and can meet comprehensive analytics requirements.

### ALD LAB DRESDEN

The ALD Lab Dresden was founded in October 2010. It is a joint venture of the Institut für Halbleiter- und Mikrosystemtechnik (IHM) of the Dresden University of Technology (Prof. Johann Bartha) and the ALD group of Fraunhofer CNT (Dr. Jonas Sundqvist) which combines their competences in the field of ALD (atomic layer deposition). The workscope is to develop new ALD precursors and processes for the semiconductor and photovoltaic industry.

### **E-BEAM INITIATIVE**

Since April 2010, Fraunhofer CNT is an official member of the e-beam initiative.

The initiative provides a forum for educational and promotional activities considering a new "designto-manufacturing" approach known as "design for e-beam" (DFEB). DFEB reduces mask costs for semiconductor components linked to designs, design software, manufacturing, manufacturing materials and manufacturer's software expertise.

# **COMPETENCE** AREAS AND **RESEARCH RESULTS**

Microelectronics is the basic technology for a lot of technical applications. The progress in the automobile and the computer industry can be owned by this technology. Microelectronic systems have to become smaller and smaller and more energy efficient. They also have to provide much more power and combine more and more new features. The key activities of Fraunhofer CNT focus on the development of innovative processes for high-performance transistors as well as the development of nanoelectronic integrated circuits to fulfill the tasks mentioned above. Fraunhofer CNT divides its groups into five areas of competences.

# **ANALYTICS**

FUNCTIONAL ELECTRONIC MATERIALS FRONT-END OF LINE

FUNCTIONAL ELECTRONIC MATERIALS **BACK-END OF LINE**

MASKLESS LITHOGRAPHY

**DEVICES & INTEGRATION**

# **COMPETENCE AREA ANALYTICS**

Group Manager Analytics

Dr. Lutz Wilde Phone: +49 351 2607-3020 lutz wilde@cnt fraunhofer de

### COMPETENCES

The competence area Analytics concentrates on the characterization of materials needed for the fabrication of modern semiconductor chips. It focuses on topics such as the distribution and activity of dopants, properties of surfaces and interfaces, crystallization and phase formation, lateral resolved stress measurements and quantification of impurities. In order to meet the challenges of ongoing miniaturization, we engage in the improvement of existing methods and also in the application of new methods, e. g. atom probe tomography.

### TRENDS

In 2011 Fraunhofer CNT continued its work on atom probe tomography (APT) in co-operation with external partners from the industry and academic research institutions. Together with our local academic partners from the Helmholtz -Zentrum Dresden-Rossendorf, the TU Dresden and the Leibniz-Institute for Solid State and Materials Research Dresden we successfully established the Advanced Atom Probe Lab and studied a wide range of materials like metallic glasses ,ODS hardened steels or pnictide based superconducting thin films.

Together with our industrial partners from GLOBALFOUNDRIES and X-Fab we are have been working on the characterization of ultrathin oxide based films used in high-K metal gate stack for high performance transistors and SONOS (Silicon-Oxide-Nitride-Oxide-Silicon) based nonvolatile memories in the framework of two publically funded projects.

Finally, a number of smaller projects have been carried out in co-operation with several partners from industrial and academic institutions that included amongst others the characterization of gallium-arsenide based materials for optical applications and materials for solar applications.

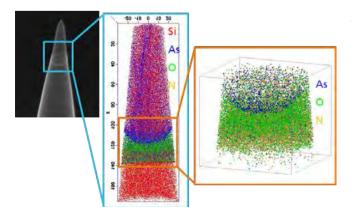

# ATOM PROBE TOMOGRAPHY

# SONOS stacks for non-volatile memory applications

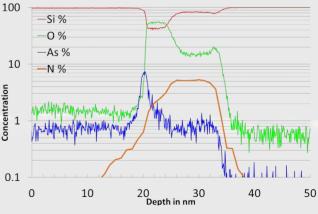

We have used APT to analyze SONOS (Silicon-Oxide-Nitride-Oxide-Silicon) based non-volatile memory cells within the publically funded project CoolAnalytics, which started in April 2011. The project aims to understand the influence of the distribution of elements within the charge trapping layer on the relevant electrical properties like charge retention, reliability and programming voltage in order to optimize the manufacturing process.

As the non-volatile memory cells under investigation are twodimensional structures and we are eventually interested to determine the concentration of silicon, nitrogen and oxygen in two dimensions as well, we need an analysis method that provides high spatial resolution and a good sensitivity. APT is the most promising method for extracting these kind of information. The major difficulty in these analyses is the mass overlap of Si<sup>2+</sup> and N<sup>+</sup> at mass 14 and Si<sup>+</sup> and N<sub>2</sub><sup>+</sup> at mass 28 respectively. We have to refer to statistical methods that separate the elements based on their isotopic distribution in order to solve this challenge.

Initial APT results from gate stacks for SONOS devices are shown in Fig. 1 and Fig. 2. Fig. 1 demonstrates that we can analyze the stack of isolating materials with APT and clearly resolve each layer. As isolating layers are notoriously difficult to analyze this is a major step in the project. The depth profile in Fig. 1 shows the thick top oxide, the thin bottom oxide and the intermediate oxy-nitride containing 5% nitrogen. Unfortunately, the oxygen guantification in the SiO<sub>2</sub> layers do not show the expected 66% oxygen. This result is likely to be caused by a combination out-gassing of oxygen during the analysis and reconstruction artifacts. . The analysis however reveals a diffusion of nitrogen into the top oxide and a strong

accumulation of arsenic at the interface between the Poly-Si electrode and the top oxide layer. Additionally, arsenic is enriched at grain boundaries in the Poly-Si covering the gate stack (Fig. 2).

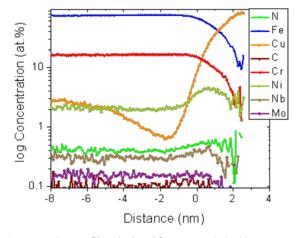

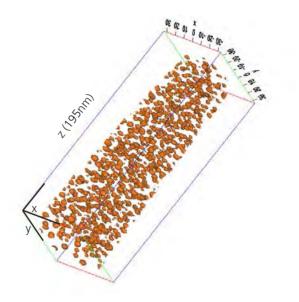

### Precipitation hardened steels

The hardening of steel by the precipitation of nano-scaled particles is a common method in steel metallurgy. APT is an ideal method to study these precipitation phenomena in detail. Together with Fraunhofer IWS (Dr. Jörg Kaspar and Dr. Jörg Bretschneider) we have investigated the martensitic stainless steel X5CrNiCuNb 16-4 hardened by Cu precipitates formed during a two-step aging process.

APT reveals the elemental composition, size, distribution and density of the Cu precipitates. The size of the precipitates was in the range of 2-6 nm diameter. The precipitate density was found to be 0.0015 nm<sup>-3</sup>, which means, that one precipitate can be found within a cube of approximately 8.7 nm length.

1 Depth profile of a SONOS layer stack showing the distribution of the main constituents.

# **ANALYTICS**

The results clearly show, that the precipitates are enriched in Cu and Ni whereas Fe and Cr are depleted compared to the matrix composition. The vicinity of the precipitates is depleted in Cu (Cu diffusion zone). A concentration profile for constituent elements as calculated from averaging over 300 precipitates is shown in Fig 3. The 3D spatial distribution of Cu precipitates in the matrix is shown in Fig. 4. Furthermore, the spatial distribution micrograph obtained using atom probe tomography reveals, that carbon is enriched at an arch-like grain boundary (Fig. 5).

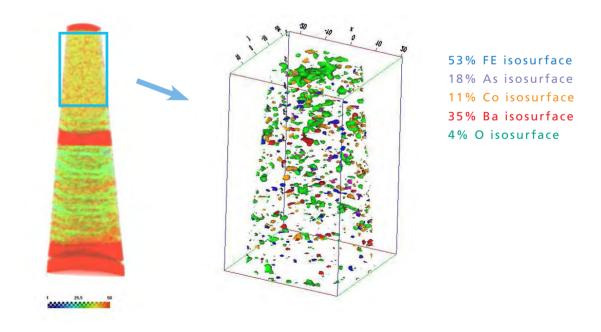

### Superconducting thin films

In 2008 a new class of high-temperature superconductors has been discovered in layered iron arsenic compounds. They are extreme type II superconductors (similar to the cuprates) of multiband nature (similar to MgB<sub>2</sub>). Since their discovery thin films of the intermetallic cobalt-doped BaFe<sub>2</sub>As<sub>2</sub> (Ba-122) phase were synthesized by pulsed laser deposition. The epitaxial growth of this compound on bcc iron offers the possibility to grow Fe/Ba(Fe<sub>1-x</sub>Co<sub>x</sub>)<sub>2</sub>As<sub>2</sub> multilayers that possess magnetically influenced superconducting and transport properties. This

**2** SEM image of a ready-to-run tip including the ROI (left) and 2d projection of 3D atomic maps of the SONOS stack (middle and right) showing enrichment of arsenic at the grain boundaries and at the top oxide.

# Matrix | Cu diffusion zone | Cu ppt

3 Concentration profile calculated from a proximity histogram averaged over 300 precipitates

layer stack has been analysed by APT in co-operation with Dr. Silvia Haindl and Jan Engelmann from IFW Dresden. In order to fabricate such multilayers for electronic applications like Josephson junctions a detailed understanding of its microstructure is needed. The investigated multilayer was grown by pulsed laser deposition under ultrahigh vacuum conditions on MgAl<sub>2</sub>O<sub>4</sub> substrates. First, an iron buffer layer was deposited at room temperature and subsequently heated up to 700°C to achieve a closed iron layer with smooth interfaces. The Ba-122 layer was grown at the same temperature. After cooling down to room temperature an approximately 5 nm thick iron interlayer was deposited and again heated up. Finally, a second Ba-122 layer was deposited at 700 °C. Epitaxial film growth was confirmed by X-ray analysis. The Fe/ Ba-122 stack is superconducting up to a temperature of 22K.

APT results show small scale inhomogeneities of the barium, iron, arsenic, and cobalt distribution in the Ba-122 film (Fig. 6). The analysed samples revealed a Co dopant gradient along the film thickness as well as Ba- and Fe-rich regions. The oxygen contamination was found to be strongest on the Fe layers.

4 3D spatial distributions of the Cu precipitates in the steel matrix

6 Distribution of the iron concentration in the layer stack (left side) and iso-concentration surfaces of iron, arsenic, cobalt, barium and oxygen showing inhomogeneities in the Ba-122 layer

5 Carbon enrichment at an arch-like grain boundary

# **ANALYTICS**

# 10

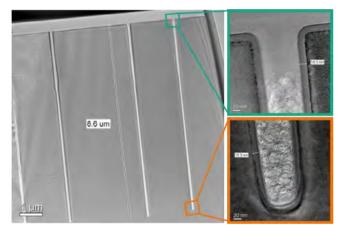

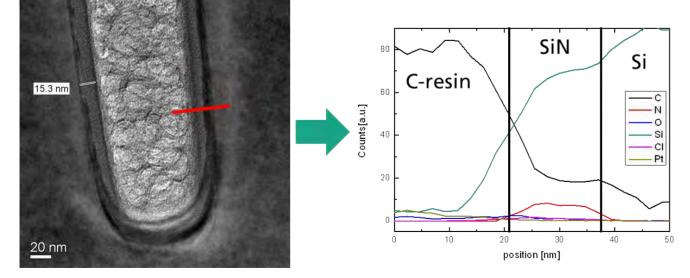

# TRANSMISSION ELECTRON MICROSCOPY

At Fraunhofer CNT, the ALD process development and the evaluation of new ALD precursors for the deposition of dielectrics is one of the core competences. TEM investigations of the step coverage of a new precursor for the deposition of Si<sub>2</sub>N<sub>4</sub> into a test structure with high-aspect ratio trenches have been carried out to support these activities. In order to reduce preparation artefacts during FIB preparation, the trenches were filled by a special resin, which shows the grainy structure in the high resolution images (Fig. 7 & 8). The ALD deposited  $Si_3N_4$  appears in middle gray. The analysis of the layer thickness at the top and at the bottom shows excellent step coverage of better than 80% (Fig. 7). A EDX line scan over the Si3N4 layer reveals, that the  $Si_3N_4$  layer is oxidized at the surface (Fig. 8).

7 Analysis of the step coverage of an ALD grown Si3N4 layer by TEM (left side: overview image; right side: top and bottom details)

8 EDX line scan over ALD grown Si3N4 layer (left side: red bar shows position of EDX scan; right side: EDX results)

# **X-RAY DIFFRACTION**

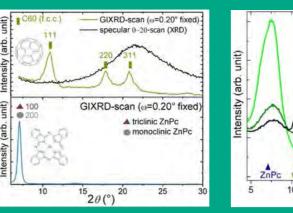

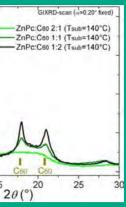

We continued with our successful co-operation on the characterization of organic thin films with Christoph Schünemann and Chris Elschner from TU Dresden, Institute for Applied Photophysics (IAPP). These films have potential applications in the field of organic electronics. Especially, we focused on the influence of the deposition temperature and the mixing ratio on the phase separation and layer morphology in blend layers of C60 and Zinc-phtalocyanide (ZnPc) which may be used as photoactive layer in organic solar cells. Due to the low layer thickness of 150nm or less, the measurements need to be carried out in grazing incidence geometry. A comparison to standard Bragg-Brentano geometry is shown in Fig. 9. While in the grazing incidence mode the reflections from the C60 film are clearly visible, in specular Bragg-Brentano geometry only the broad hump from the glass substrate is visible. Both molecules have a different shape, as shown in the inset of Fig. 9a, leading to the formation of separated C60 and ZnPc domains. Enhanced phase separation was observed for higher C60 contents and for higher growth temperatures resulting in improved charge carrier percolation paths and therefore improved solar cell performance. The GIXRD measurement clearly indicates that even for high ZnPc content within the blend, ZnPc is not able to crystallize, even for elevated substrate temperatures of 140°C (Fig. 9).

# **TOF-SIMS**

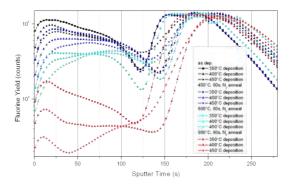

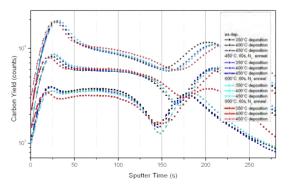

The deposition of 5 nm thin TaCN films from tetramethyldisilazane (TDMS) and TaF5 precursors on Si substrate by an ALD process was studied by ToF-SIMS measurements. These films are used as etch stop layers in the replacement gate technology for the sub-28 nm node. The ToF-SIMS measurements are performed to determine the influence of the deposition temperature and the temperature of a subsequent post deposition anneal (PDA) on the carbon and fluorine concentration within the film. From the measurements it is obvious, that the PDA temperature has a significantly higher influence on the fluorine contamination within the film than the deposition temperature (Fig. 10). The decreasing fluorine concentration upon higher PDA temperature can be attributed to outgassing of fluorine. Otherwise, the carbon content is almost independent of the PDA temperature but shows a significant dependence on the deposition temperature as shown in Fig. 11. The N/C ratio (N not shown here) increases with increasing temperature of deposition due to the growth behavior of the ALD precursors.

10 Depth profile of the fluorine intensity in dependence of PDA and deposition temperature

**9** GIXRD scans of pristine C60 and ZnPc films (left) GIXRD scans of heated blend layers with different ZnPc:C60 ratio (right)

11 Depth profile of the carbon intensity in dependence of PDA and deposition temperature

Group Manager Functional Electronic Materials - Front End of Line (FEoL):

Dr. Malte Czernohorsky Phone: +49 351 2607-3032 malte.czernohorsky@ cnt.fraunhofer.de

# FUNCTIONAL ELECTRONIC MATERIALS FRONT-END OF LINE

# COMPETENCES

Objective of this research area is the development of insulating, semi-insulating and conductive thin films. These materials are suitable for various applications in micro- and nanoelectronics. One of the core competencies of the group is the Atomic Layer Deposition (ALD) of dielectric and conductive layers on 300 mm silicon wafers. The broad spectrum of ALD research activities covers different technical areas: ALD precursor testing, hardware and equipment evaluation as well as material and process development for high-volume manufacturing. Fraunhofer CNT works in close collaboration with industrial and academic partners. Hence, the Dresden ALD community established the "ALD Lab Dresden" as a common platform in fall 2010.

# TRENDS

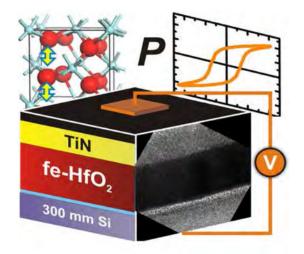

The focus of our R&D activities are high-k/metal gate (HKMG) stacks for coming generations of field effect transistors (FET) and high-k dielectrics and electrodes for non-volatile memories (NVM) and MIM-based capacitors. In the field of ferroelectric memories (FeFET) Fraunhofer CNT made a significant contribution through the engineering of ferroelectric hafnium oxide (HfO<sub>2</sub>) creating the "most aggressively scaled" FeFETs using ferroelectric Si:HfO<sub>2</sub> in a 28 nm HKMG stack (TiN/Si:HfO2/SiO<sub>2</sub>/Si). Fully functional FeFETs could be fabricated fulfilling current Flash specification in terms of data retention and endurance, but with much lower power consumption and DRAM-like write/erase speed. MIM capacitors are used in stand-alone and embedded DRAM and as integrated passive devices for RFCMOS. In 2011, we optimized the interfaces in the MIM stack to further improve the linearity of the TiN/ZrO<sub>2</sub>-based capacitors. In addition, we developed a low cost tantalum carbo nitride (TaCN) ALD process on a large batch furnace. Beside the usage in the Replacement Gate transistor technology this process can be used also for memory applications in high-volume manufacturing (e.g. MONOS Flash) and heater electrodes for phase change memory (PCRAM).

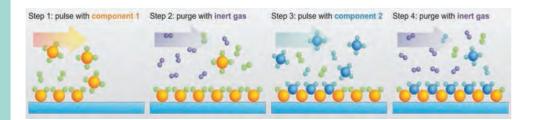

1 The ALD cycle of a metal oxide deposition is composed of the following steps: metal-containing precursor pulse (step 1), purge of non-reacted precursor and reaction products with inert gas (step 2), oxidant pulse e.g. ozone or water (step 3) and a second inert gas purge to remove reaction products (step 4). The sequence is repeated several times to achieve the desired film thickness.

# **METAL NITRIDES**

Since its release in the early 1950's the transistor has undergone a continuous scaling process. The recent problem of leakage current through the ever shrinking silicon dioxide gate dielectric was tackled with the introduction of new high-k dielectric materials such as hafnium dioxide together with metal gate electrode materials such as metal nitrides. Using the Replacement Gate technology, metal nitrides are deposited by ALD, as the small feature sizes require conformal film growth. For further structuring of pFET and nFET, an etch stop layer is required within the metal gate film stack.

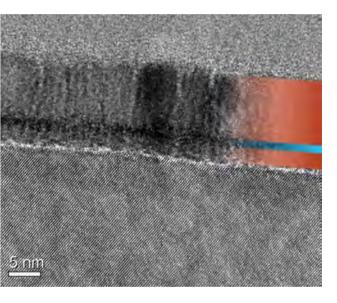

The deposition of a tantalum nitride based etch stop layer and diffusion barrier via 300 mm batch furnace ALD was developed at Fraunhofer CNT. The film showed a high growth rate and very conformal growth with very little surface roughness. Thorough material characterization confirmed etch-stop and diffusion barrier properties of the deposited TaCN films, as required for film in the Replacement Gate process flow.

Together with the process of titanium nitride ALD, a batch furnace in-situ process was then developed for the deposition of a complete TiN-TaN-TiN metal gate stack for the integration into the replacement gate process flow. The in-situ deposition enables well controlled interface treatments in between the metal films, as well as a low cost of ownership due to the high throughput of the batch furnace. This ALD process enables further transistor scaling below the 28 nm node for future Replacement Gate applications.

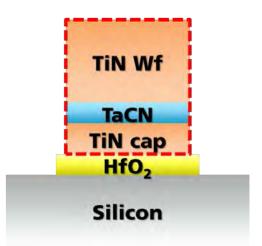

2 HRTEM of a TiN-TaCN-TiN metal gate film stack deposited in-situ via ALD on the ASM A412 large batch furnace (red: TiN, blue: TaN).

3 Replacement Gate Stack schematic: TiN Wf - workfunction layer to control gate work function, TaCN - etch-stop and diffusion-barrier layer, TiN cap - capping layer to control interface to gate dielectric

# FUNCTIONAL ELECTRONIC MATERIALS - FRONT-END OF LINE

# FERROELECTRIC FIELD EFFECT TRANSISTORS FOR FUTURE MEMORIES

Microelectronics and data storage technologies in particular, are strongly dependent on the ever-progressing strive to smaller feature sizes. Only then the cost savings in mass production are achieved necessary to remain competitive in a market of rapidly increasing storage density. Thus, in analogy to the aggressive scaling of logic transistors, the device density per unit area of the high-volume segments SRAM, DRAM and FLASH continuously increases with each new technology introduced. Nevertheless, despite their high scalability those conventional technologies are in many aspects inferior to new, innovative store concepts. The diversification of storage applications (mobility, cloud computing, long term storage, etc.) makes room for new storage technologies, generally summarized as "emerging memories".

The individual combination of memory properties with respect to nonvolatility, speed, power consumption, endurance and scalability gives concepts such as STT-MRAM(magnetic RAM), RRAM(resistive RAM), PCRAM(phase change RAM) and FRAM (ferroelectric RAM) a clear edge over the aforementioned mass memories. However, regarding power consumption during switching operation the FRAM, even in the field of emerging memories, has to be accentuated. Especially in the case of 1T FRAM (ferroelectric field effect transistor FeFET) the switching process is limited to a simple field-effect whose power consumption in relation to the current-driven switching in the STT-MRAM, RRAM and PCRAM has a vanishingly low energy consumption.

The successful integration of such an energy-efficient storage device into industrial production, however, had been considerably more difficult than expected and was limited by the available of integrated ferroelectric materials. Already known ferroelectrics such as lead-zirconat-titanate (PZT) or strontium-bismut-tantalate (SBT) lack back end of line (BEOL) stability, full CMOS compatibility and suffer from a high

1 Conventionalized gate structure of a HfO2-based ferroelectric field effect transistor.

physical-layer thickness (low coercive fields, high dielectric constant) that only with considerable effort can be integrated into a conventional process flow. However, with the successful stabilization of ferroelectricity in HfO<sub>2</sub>, a material system already well-known to microelectronic engineering, a new approach and therewith a new perspective for highly scaled, ferroelectric memories has been demonstrated. Scientist of the Fraunhofer CNT have identified several strategies to form ferroelectric HfO<sub>2</sub> and in the course of the projects MERLIN and HEIKO developed large expertise in depositing, structuring and characterizing those novel ferroelectric materials.

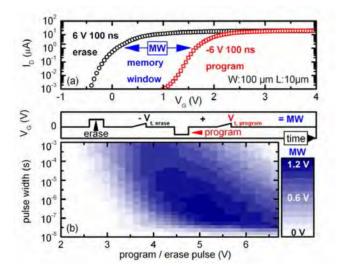

Currently the integration of an actual memory device based on an HfO<sub>2</sub> based ferroelectric field effect transistor has reached a final stage. In cooperation with our long term partners GLOBALFOUNDRIES and Namlab gGmbH fully functional ferroelectric field effect transistors on a state of the art 28 nm ground rule have been demonstrated.

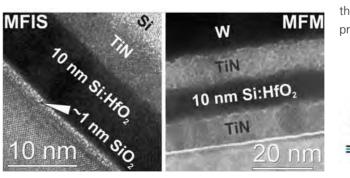

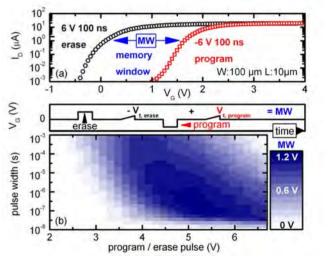

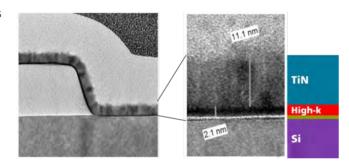

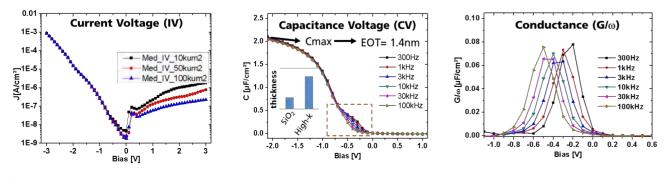

Figure 2 depicts TEM cross sections of the gate stack of an earlier but comparable ferroelectric device, as well as a ferroelectric MIM capacitor used for process qualification and ferroelectric parameter extraction. Basic device operation was statistically verified and is representatively depicted in Figure 3a. Endurance comparable to current Flash technologies as well as data retention exceeding 10 years was further demonstrated. Additionally, outstanding switching times below 20 ns were achieved as can be seen in the time and field dependent memory window matrix in Figure 3b. In summary this predicts a fast, highly scaled, non-volatile memory concept based on a highly engineered, ferroelectric HfO<sub>2</sub>. In current and future

**3** Basic device operation of a ferroelectric field effect transistor (a). Time and field dependence of ferroelectric switching and its impact on memory window evolution.

projects a 100 bit demonstrator will be fabricated representing the final step in putting the newly discovered ferroelectric properties of  $HfO_2$  to a useful application in industrial scale.

ALD Lab Dresden

# FUNCTIONAL ELECTRONIC MATERIALS - FRONT-END OF LINE

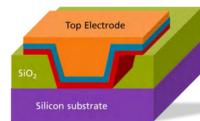

# **HIGH-K MATERIALS FOR MIM CAPACITORS**

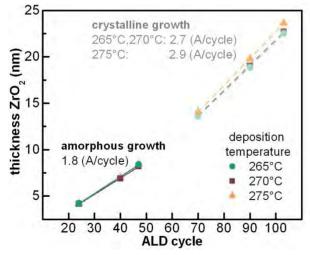

ZrO<sub>2</sub> is of very high interest in semiconductor industry mainly as high-k dielectric in DRAM, eDRAM or even resistive RAM. Above all, no alternative materials are in sight for the next generations of DRAM. Thus, further improving of deposition processes, of material properties and of integration schemes is essential to meet the strict requirements of future devices. One key challenge is reducing the process time of the bottle neck high-k ALD deposition. The most common process used for ZrO, deposition is TEMAZ/O, with a published growth rate of 1 Å/cycle. Thereby, the  $O_3$  process causes oxidation of the TiN bottom electrodes resulting in MIM capacitor asymmetries and capacitance linearity issues. At the Fraunhofer CNT, we improved the TEMAZ/O<sub>3</sub> ALD process and studied the growth and crystallization behavior of thin ZrO<sub>2</sub> films. A growth rate of 1.8 Å/cycle up to 2.7 Å/cycle could be achieved by increasing the TEMAZ and the O<sub>2</sub> pulse times (Figure 1). Linear growth and good uniformity on 300 mm wafers could be proved for an ALD window up to 270 °C which is comparable to published TEMAZ/O<sub>3</sub> processes. The increase of the growth

1 Linear growth of  $ZrO_2$  from a new TEMAZ/O<sub>3</sub> process at different deposition temperatures.

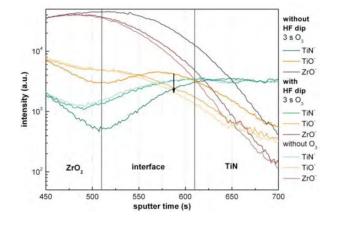

2 ToF-SIMS depth profile of the interface between ZrO2 and TiN after different interface treatements.

rate correlates to the crystallization of the ZrO<sub>2</sub> films during deposition starting at a critical film thickness. Besides the fast growth rate the deposited ZrO, layers show very good electrical performance with a CET of 0.7 nm and a leakage current of 2.6 • 10<sup>-9</sup> A/cm<sup>2</sup> at -1 V for a 7 nm thick crystalline film. Additionally, the new ZrO, ALD process was used to optimize the integration scheme of MIM capacitors with TiN electrodes addressing the bottom interface between ZrO, and TiN. In a first step, the TiN surface was studied in detail after an HF-Dip by XPS and Rs measurements to implement a time coupling between TiN and ZrO<sub>2</sub> deposition. Interestingly, the native TiO, can be reduced but never removed completely. In a second step, the influence of the O<sub>3</sub> oxidation was minimized by several process variations including lower O<sub>3</sub> pulse times or skipping the O<sub>3</sub> pulse only for the first cycles of the ALD deposition. AR-XPS and ToF-SIMS depth profiles show a significant decrease of the TiO, between ZrO, and TiN by using an HF-Dip. This reduction is intensified by the ZrO, process without O<sub>2</sub> which is visible by the decrease of the TiO-ion at the interface between ZrO<sub>2</sub> and TiN in Figure 2.

Group Manager Functional Electronic Materials -Back End of Line (BEoL):

Dr. Romy Liske Phone: +49 351 2607-3040 romy.liske@cnt.fraunhofer.de

# FUNCTIONAL ELECTRONIC MATERIALS -BACK-END OF LINE

# COMPETENCES

15 years ago, a remarkable step was taken by implementing copper as metallization material in the fabrication of integrated circuits (ICs). It was not only the change of material from aluminum to copper but rather the whole integration scheme, changing from the subtractive structuring method to the damascene process, that challenged engineers and scientists. However, especially the integration of new processes like CMP (chemical-mechanical planarization) and the development of new material combinations proved the superiority of copper against aluminum metallization.

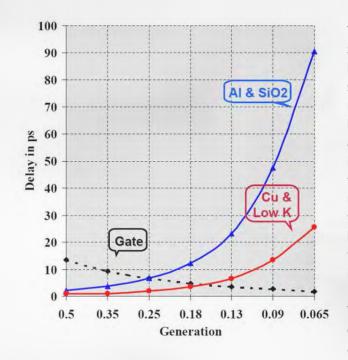

In the early years of chip manufacturing, the transistor size determined the processor clock rate. A decreased gate length allowed a shorter switching time, which made the processors faster and faster. However, a side effect of shrinking gate lengths is that the area available for electrical contacting is reduced as well. The wires as well as the spaces between them get smaller and reach the dimension of actual copper grain sizes, leading to a non-linear resistivity increase as well as increased capacitance effects. That means, nowadays, the signal propagation rate through the electrical wires limits the processor clock rate, since it passed the transistor switching time delay (Figure 1). Thus, the main task for research and development in the back-end of line is to minimize the RC delay. This is addressed through all different processes in the back-end of line module at the Fraunhofer CNT.

1 RC delay influence of front-end of line transistor and back-end of line interconnects. Effect of change to copper and low-k. From: Bohr; "Interconnect Scaling – The Real Limiter to High Performance ULSI"; Proceedings of the 1995, IEEE International Electron Devices Meeting.

The capacitance C can be decreased by using low-k materials as dielectrics. Besides changing the material type, porosity can be introduced to further decrease the k-value. However, a porous material increases the integration complexity, because all connected processes need to be tuned as to minimize the damage of the porous material itself and the k-value degradation. Furthermore the mechanical strength of porous low-k material can be challenging.

At the Fraunhofer CNT research focus has been put on the sidewall damage of the low-k due to the RIE etch, the influence of wet clean processes after dry etching and the possibilities of restoring k-values through repair processes. For the future it is intended to investigate the influence of CMP processes on the k-value.

The resistivity R depends on the materials used for metallization and their microstructure. State-of-the-art material for leading edge interconnect technology remains copper. Its specific resistivity is low (1.7  $\mu\Omega$ cm) and electro- and stress migration are sufficient. However, copper needs an efficient barrier to prevent it from diffusion into the interlayer dielectric and to prevent it from oxidation. It is the aim of interconnect integration to use as much copper for the circuit as possible for performance and as little barrier as absolutely needed for reliability. As the cross-section of connects for leading edge technology nodes is in the order of copper grain sizes and the barrier uses a significant area fraction, barrier material reduction and void-free copper filling with optimized microstructure is demanded.

Thus at the Fraunhofer CNT focus is on the development of new CVD-deposited barrier materials, that allow a thin and conformal deposition with good sidewall coverage. Preferably, these barriers have value added properties like good conductance to omit a seed layer for copper deposition, which, together with a void-free copper superfilling by electrochemical deposition, leads to a better copper microstructure and thus faster and more reliable circuits. The role of the bath additives in electrochemical plating, which are responsible for superfilling, is subject of research at the Fraunhofer CNT. Furthermore the influence of the annealing regime on the copper microstructure can be studied.

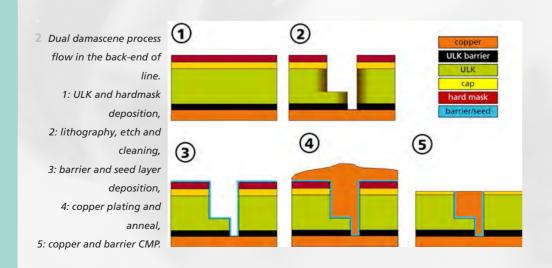

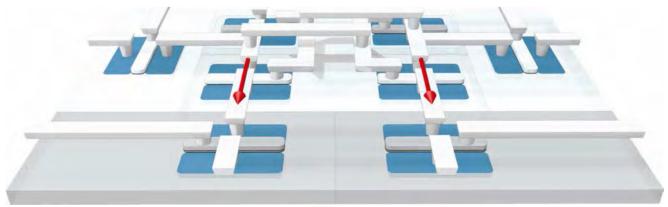

In the near future process development in the field of chemical-mechanical planarization in interconnect technology can be carried out. Topics of interest will cover polishing of new barrier materials with low damage stop on low-k dielectrics. The back-end of line process flow is shown in Figure 2. Leading edge research in the Fraunhofer CNT covers ULK etch, clean, barrier and seed deposition, copper plating and CMP.

# **FUNCTIONAL ELECTRONIC MATERIALS - BACK-END OF LINE**

# **INTEGRATION OF ULK-PERFORMANCE**

### ULK Etch – Structuring of the Patterns

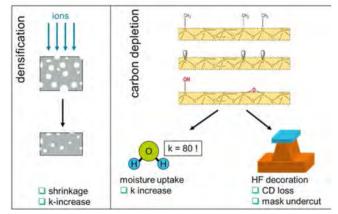

Vias and trenches in the dielectric are formed by reactive ion etching. The complex etching process proves to be especially challenging for low-k and ultra-low-k materials. These new dielectrics introduce carbon to lower the polarizability and thus the k value down from 4 (traditionally used SiO<sub>2</sub>) to about 2.7 for low-k materials. By adding pores, the so called ultra-low-k (ULK) materials achieve k values as low as 2. However, low-k materials come with several integration challenges, especially for the etching and resist ashing processes, which cause damages in the microstructure and alter the materials properties. Challenges are:

- Profile and CD control

- Change of dielectric properties by plasma induced damage leading to increased k value, which impacts the electrical performance

- Pore diffusion, moisture uptake, metal barrier precursor diffusion

- Sidewall and bottom surface roughness

- Mask integration

- o Metallic hard masks: wiggling, µ-masking, metallic residues

- o Organic resists: ashing, resist poisoning

Plasma damage can be divided into two mechanisms. The physical damage results from ion bombardment in the plasma. In low density porous low-k materials this leads to a densification and hence to a shrinkage and an increase in the k-value. The chemical effect plays a more important role in the trench sidewalls. Here, the methyl groups of the ULK material (which are responsible for the lower k-value) can be removed by the

1 Damage mechanisms during ultra-low-K etching.

species in the plasma. This leads to dangling bonds or formation of hydroxyl groups at the surface. The result is a much more polar surface which leads to a much higher probability of water adsorption. With the adsorbed water (k-value of 80!) the effective k of the ULK material rises. Additional problems arise when the damaged ULK material is exposed to the subsequent cleaning step. Because damaged ULK is chemically similar to silicon dioxide, the cleaning step by hydrofluoric acid attacks the altered dielectric. This material removal can cause issues like hard mask undercuts or CD loss and further difficulties with the barrier layer deposition afterwards.

During an extensive project together with Globalfoundries details about the damaging of the ULK material by the etch process are investigated. Several advanced plasma diagnostics are available like high-resolution optical emission spectroscopy, quadrupole mass spectroscopy and quantum cascade laser absorption spectroscopy. Using these methods helps to understand the details of the processes, e.g. by detecting plasma species in the excited state and in the ground state.

Through our close cooperation with Globalfoundries and our equipment (300 mm industry standard) a complete back-end of line integration is possible. Processed wafers can be send back to Globalfoundries for further processing or for the measurement of electrical data, which provide the ultimate benchmark for refined or newly developed processes.

### ULK Clean – Removing Etch Residues

After etching vias and trenches, the next step is usually a wet clean. Residues from hard masks, remaining resist or fluorine polymers formed on the sidewalls have to be removed to enable a clean and conformal deposition of the barriers afterwards.

Several different cleaning chemicals, water or solvent based are evaluated with special emphasize on compatibility with the ULK material, copper and the barrier layers. Since the structures get smaller and smaller, good surface wetability has to be assured. Adding surfactants and optimizing process parameters for chemistry application and rinsing steps can improve the overall performance of the ULK cleaning step.

### ULK Repair - Restoring the k-value

Though the etch process can be optimized to result in minimal damage of the ULK material, it may not be possible to completely keep the pristine structure of the dielectric. The aforementioned carbon depletion and water adsorption can be faced by chemical sylilation repair processes. Here polar hydroxyl groups are substituted by methyl groups and the original ULK structure and thus the k-value can be restored.

Similar to the cleaning step different repair chemicals can be screened to find the optimal process parameters. Additional pre annealing to remove adsorbed water and post curing by UV as well as IR radiation to remove unbound fragments and to promote cross linking can be used.

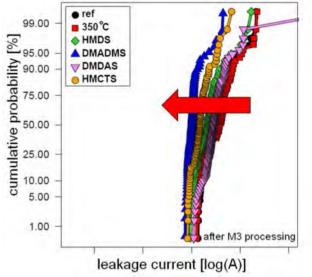

2 Improvement of leakage current by low-k repair.

# **ULK Characterization – Observing material changes**

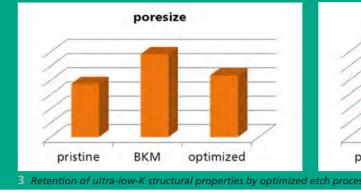

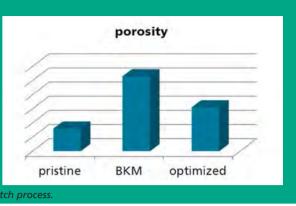

Furthermore there are multiple options for advanced ULK analytics. A unique tool is ellipsometric porosimetry which enables pore size and porosity measurements. Additional information about the Young's modulus or diffusion barrier integrity can also be obtained. Via different TEM options like EELS or EDX the carbon loss in the ULK material which is associated with plasma damage can be measured. Finally by FTIR the character of the chemical bonds in the ULK material can be identified.

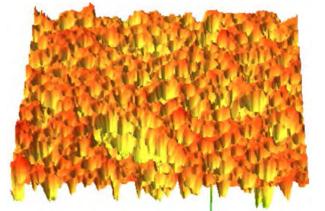

By optimizing existing 'best known methods' (BKMs) recipes an improvement for the etching of the ULK layers can be achieved. The optimized processes yield ULK films with a structure much more similar to the pristine one, in terms of pore size or porosity, while maintaining a comparable etch rate (Figure 3).

# **FUNCTIONAL ELECTRONIC MATERIALS - BACK-END OF LINE**

# **COPPER DIFFUSION BARRIERS SCALING**

The transition to the Cu/ULK node induced a need for the development of novel diffusion barriers preventing the intermixing of copper with the adjacent dielectric layer and other regions on the chip. They should be compatible with current integrated circuit fabrication flows. At the same time the material used needs to be thermal and structural stable and also highly thermally and electrically conductive.

The present state-of-the-art barrier/adhesion promoter used in the back-end of line is a Ta/TaN film stack. However, despite its excellent barrier properties, this material combination has also some limitations. One of them is given by the fact that both, the Ta and TaN are deposited by physical vapor deposition (PVD). This deposition technique does not comply with the stringent step coverage requirements for features having critical dimensions. Furthermore, the copper plating can not be conducted direct on the Ta layer. First a seed layer has to

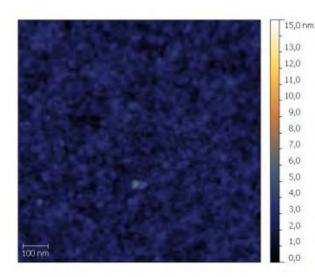

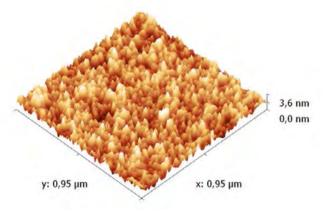

1 A AFM measurement of a 7.5 nm thick cobalt layer.

be deposited. By this way the trench fraction that is filled with bulk copper is reduced and the resistivity of the whole interconnect structure increases.

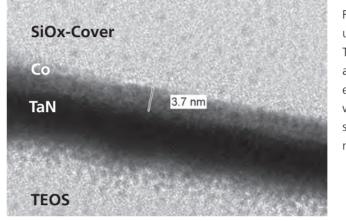

To overcome these limitations Fraunhofer CNT and GLOBAL-FOUNDRIES have joint their efforts to enable chemical vapor deposited (CVD) cobalt as the diffusion barrier of choice for sub 28 nm technology nodes, see Figures 1 and 2 for topography measurements by AFM and a TEM cross section, respectively. Compared to Ta it has a much lower electrical resistivity and higher thermal conductivity, but the greatest benefit of introducing Co as a barrier material is given by the fact, that it can be deposited by CVD and the Cu plating can be conducted directly on its surface.

In this way the step coverage of structures with critical dimensions can be improved and the trench fraction filled with bulk copper, thus the electrical conductivity of the conductor path can be increased.

2 TEM of a Co layer deposited on TaN.

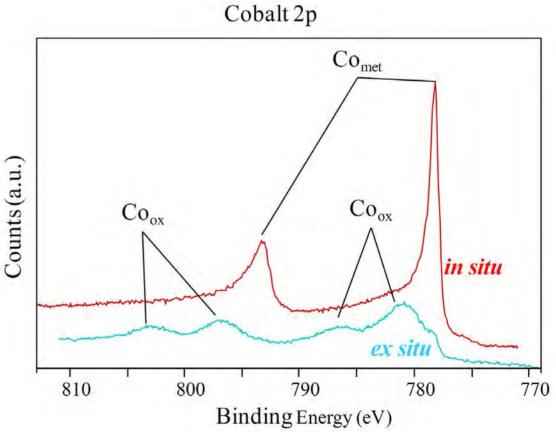

3 In situ and ex situ XPS measurement of a cobalt layer.

For process development and optimization Fraunhofer CNT uses a state-of-the-art AMAT Endura2 tool having Degas, PVD Ta/TaN, PVD Cu RFX and CVD Co chambers. One additional advantage is given by the in situ XPS measurement system enabling chemical analysis of the deposited thin film layers without breaking the process vacuum. The importance of in situ XPS is shown in Figure 3: exposure to air during ex situ measurements leads to a rapid oxidation of the Co surface.

# **FUNCTIONAL ELECTRONIC MATERIALS - BACK-END OF LINE**

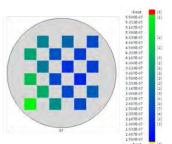

# FROM POLISHING TO HIGH PERFORMANCE PLANARIZATION

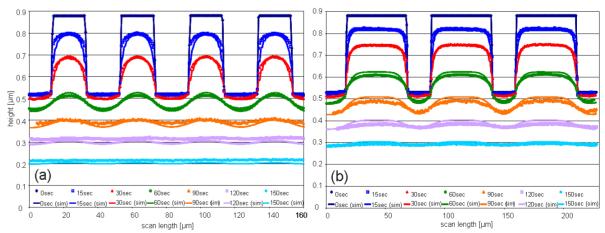

As the size of modern integrated circuits continues to shrink, the planarity of structures after CMP becomes more and more important. As a result, a better understanding of the relevant mechanisms affecting planarization is needed in order to meet future process specifications.

The planarization of a patterned wafer is characterized by the interaction of numerous variables such as applied pressure, relative velocity between pad and wafer, pad (roughness, hardness, elastic modulus, etc.) and slurry characteristics. In respect to pad surface roughness, a conditioning process is performed in order to remove debris from the pad surface, restore pad surface quality and thus to achieve high and stable removal rates from wafer to wafer.

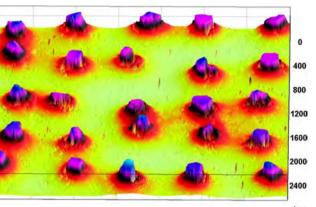

Thus, a small amount of pad material is continuously removed and the specific pad surface properties are established. Because only this modified upper pad layer, defined as 'asperity layer', contacts the wafer during polishing, it has a large

impact on the quality of the CMP process. To characterize the interrelation between conditioning and pad surface texture, a novel roughness characterization methodology has been developed. It is capable of extracting important contact mechanical parameters like the mean asperities radius of curvature, the asperity height and size distribution. These pad properties can be linked directly to process characteristics like removal rate, defect density and planarization performance in CMP and thus be used for consumables testing and optimization (Fig. 3).

Another topic in which the Fraunhofer CNT has large experience is the characterization of the CMP planarization performance. For this, the influence of consumables like slurry, pad or conditioner on the planarization of specifically developed CMP test-wafers is systematically examined and evaluated using in house developed analysis routines.

Stringent requirements of newest technology nodes as well as the transformation of traditional IC manufacturing towards

2 CMP equipment at the Fraunhofer CNT: (left) Applied Materials Reflexion LK; (right) Stangl mobile slurry systems.

foundry businesses with a wide and rapidly changing product portfolio, in extreme cases with little quantities, the ever decreasing time to market and shortened product life time of chip generations, all these demand a well-aligned CMP design and process. Thus a CMP-aware design becomes more and more crucial to be capable of competing on the market.

Novel CMP modeling approaches are a powerful tool for achieving this goal by enhanced process understanding, therefore enabling new integration paths, precise design rules with fill strategies and cost effecient process development. The Fraunhofer CNT has great knowledge in the characterization of planarization processes with the help of patterned CMP test chips (Fig. 1). The data collected is used to build up chip and feature scale CMP models, which are capable of simulating the characterized planarization process. Such calibrated models can be used on real production layouts to identify hot spots and support smart fill strategies or suggest design changes before the production of the mask sets.

> 3 Confocal measurements of a conditioner (top) and a 1 mmx1 mm conditioned pad sample (down).

4 (left) Measured (symbols) and modeled planarization of test structures with 20 μm line width, 20 μm space width and 50 % density. (right) Measured (symbols) and modeled planarization of test structures with 50 μm line width, 20 μm space width and 71.4 % density.

Structures used for process characterization.

(a) density field 1,

(b) pitch field,

(c) density field 2.

white: up-regions,

black: down-regions

400 800 1200 1600 2000 2400 x/µm

Group Manager Patterning

Dr. Christoph Hohle Phone: +49 351 2607-3013 christoph.hohle@cnt.fraunhofer.de

# **COMPETENCE AREA** MASKLESS LITHOGRAPHY

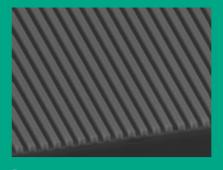

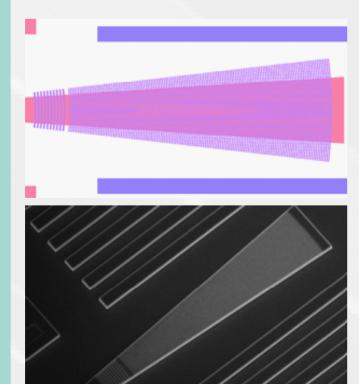

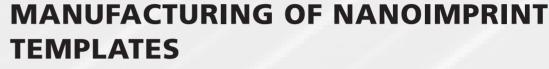

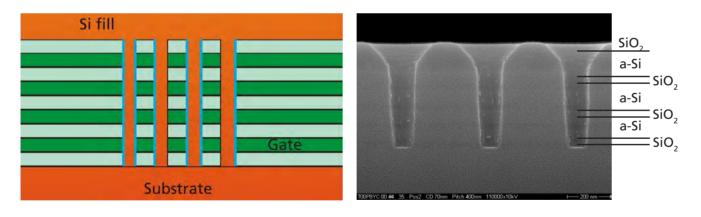

2 Imprint template structures transferred into silicor

### **COMPETENCES**

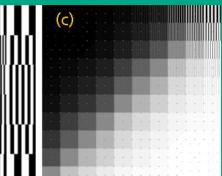

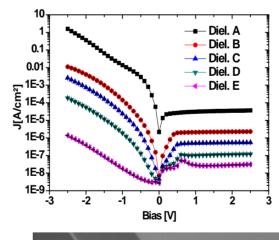

The competence area "Maskless Lithography" provides manufacturing of resist masks in special organic photoresists with patterning sizes down to 35 nm and their transfer into the underlying hard mask. Exposure is carried out using maskless electron beam lithography. The competence area focuses on the preparation of customer and application-specific designs and layouts on 200 mm and 300 mm wafers via a modern and flexible direct patterning process.

### TRENDS

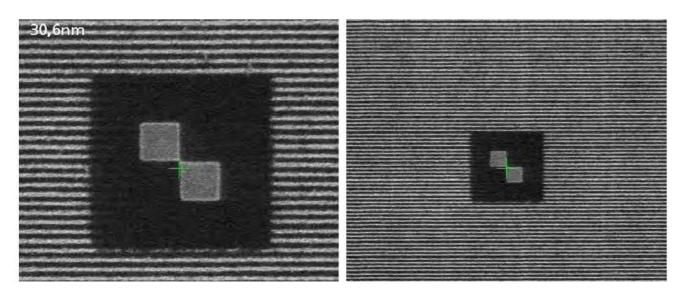

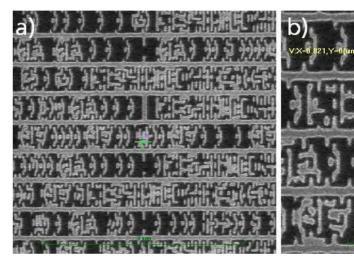

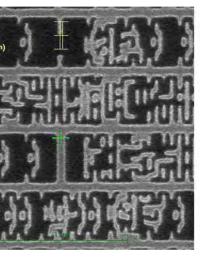

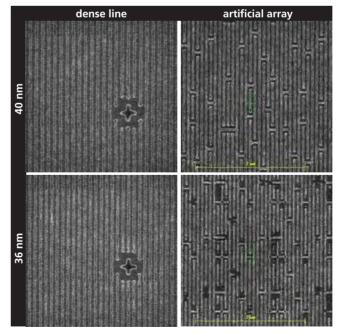

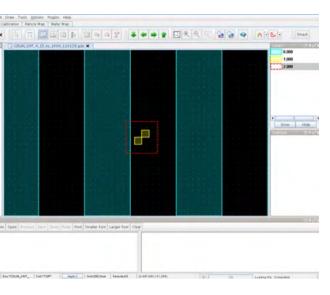

In 2011, Fraunhofer CNT's patterning capabilities have been extended to meet customer requirements according to high resolution "More-Moore" applications but also for novel "More-than-Moore" challenges. Research in the field of e-beam patterning has been intensified regarding resist resolution, data prep and proximity effect correction (PEC) as well as most advanced e-beam lithography processes on customer specific substrates and stacks.

3 Optical coupling as designed (left) and as final imprint template (down)